便携式设备中的关键电源管理电路设计

由于集成的功能不断增多以及外形尺寸的日益缩小,最新一代功能丰富的更小型便携式设备将使电源管理设计发挥关键作用。一般来说,便携式设备主要包括微处理器、I/O外设、LED背光、闪存和/或硬盘驱动器(HDD)、数字和模拟电路,这些功能模块对电源的要求各不相同。为使这些功能模块正常工作并最小化功耗以实现更长的电池使用时间,系统设计工程师面临如何设计嵌入式电源管理解决方案以满足电源要求的挑战。本文对电源要求进行了分析,并重点阐述如何设计这些电源管理电路。

为微处理器供电

微处理器是处理各种数据和命令的核心器件,大多数微处理器都采用CMOS电路并具有开关功耗和静态功耗。数字电路的每一次开关转换均对数字电路的输出电容进行充放电,由此产生的功耗由下式表示:

其中,C为总负载电容,fS为开关频率,VCORE为施加在微处理器上的电源电压。根据此公式得知:时钟频率的降低将使功耗呈线性下降,电压的降低可导致功耗呈二次方程式下降。随着微处理器处理速度越来越快,施加在微处理器上的电压将降低小于1V以最小化功耗。

微处理器最常见的供电电压范围为1.0~1.5V。从电压要求来看,大多数微处理器都具有严格的电压容差,在稳定状态和负载瞬态时的电压容差不到100mV。由于微处理器对低工作电压和大电流(具有大的边沿斜率)的要求,电源管理设计工程师面临既要满足严格的电压瞬态要求,又要解决系统功耗预算和电池运行时间(高转换效率)的难题。微处理器的功耗通常为系统总功耗的30~40%左右。通常为便携式设备供电的锂离子电池,采用LiCo02阴极材料,其典型的电池工作电压范围介于3.0~4.2V。

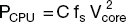

图1所示的同步降压转换器拓扑能有效地将电池电压转换为低内核电压。通常,具有集成MOSFET的固定频率脉宽调制(PWM)DC/DC转换器在正常负载条件下具有90%以上的转换效率,但由于开关损耗和栅极驱动损耗的影响,它们在轻负载条件下(如便携式设备的待机模式)的效率较低。为使便携式设备实现超长的电池待机时间,转换器能在轻负载条件下提供高效率非常重要。

图1:(a) 同步降压转换器拓扑结构图;(b) 负载瞬态过程中的负载电流和电感电流

首先是要设计降压转换器工作在非同步模式,这样就避免了因尽量减少与回路电流有关的传导损耗而导致的负电感电流。此外,脉宽频率调制或脉冲跳跃(pulse skip)模式通常用于最小化栅极驱动和开关损耗。诸如TI开发的节电模式等专用技术通过关闭部分控制电路来降低开关损耗,并使PWM控制器的静态电流最小。在150μA的负载条件下,可以实现低至18μA的静态电流和超过70%的效率。

然而,对从轻负载到高负载的负载瞬态而言,这种降压转换器带来了另一个挑战,即它需要一个延迟时间来唤醒PWM控制器并使其进入工作状态。在此延迟时间内,输出电容必须为负载供电,这将引入一个与固定频率PWM转换器有关的额外电压降。如何克服节电模式带来的这一负面影响呢?微处理器的电压规范允许具有±5%的总容差,其中包括稳定状态误差和负载瞬态。可以将轻负载时的输出电压提高1%左右,以补偿由于控制电路唤醒延迟引起的额外压降。

事实上,对移动处理器而言,提高轻负载时的输出电压是一贯的做法,这一做法被称为负载线调节。这种技术增大了瞬态电压的摆幅,因此它允许对额外电压降进行补偿或使用更小的输出电容。此外,控制环路设计和电感设计对电压瞬态响应的影响非常大。那么,如何选择正确的电感和设计控制环路带宽来实现快速的瞬态响应,并在保持高效率的同时满足电压瞬态要求呢?

对从小于1mA负载到满负载的阶跃负载瞬态而言,电压瞬态响应通常应在±3%以内。当阶跃负载被施加到系统和输出电容时,该电压瞬态与等效串联电阻(ESR)和转换延迟密切相关。通常情况下会采用小型ESR陶瓷电容,因此,通过优化环路设计和电感值来最小化输出电容器两端的电压瞬态最具挑战性。输出电容器需要在瞬态响应期间提供负载电流。微处理器所需电流的斜率比降压转换器电感电流的斜率大得多。负载电流和电感电流之间的差决定了需要由输出电容提供的电荷数量,如图1(b)所示。如果可以减少该非平衡电荷,则能降低瞬态电压,减小输出电容。电感电流的斜率越大,瞬态响应就越快,压降也就越低,因此瞬态响应取决于电感电流跟随负载电流的方式。电感电流上升时间与此处描述的控制环路带宽密切相关。

其中,fC为闭环环路带宽。另一方面,反馈控制环路在轻负载到高负载转换期间使占空比加大,在电感两

- 支持汽车电子的嵌入式软件编程接口库设计(11-29)

- 用IXP网络处理器设计的数字家庭媒体中心系统 (02-12)

- 基于DSP和CPLD的智能相机系统设计与研制(08-19)

- 基于DM642嵌入式无线视频监控硬件设计 (10-15)

- 基于AD7892SQ和CPLD的数据采集系统的设计(11-10)

- 嵌入式向产业上游迈进(01-06)