调试设计:芯片设计中必不可少之举

时间:06-25

来源:半导体国际

点击:

测试与调试分别有不同的问题。在测试中,目的是要尽快确定芯片是否以较高的稳定性正常工作,而不是绝对的稳定性。现在芯片设计团队普遍认识到,这需要在芯片上添加DFT(可测试设计)电路。第三方工具和IP (知识产权)企业可帮助实现此目标。

而调试则完全不同了。调试的目的并不只是简单地确定芯片出现了故障,而是要找出故障的原因。这种检查并不限于在测试台上的几秒钟,可能要持续数周时间。它并不是自动进行的,而是需要芯片设计团队的参加。它出现在设计周期中的离散点上:在第一个芯片设计阶段、在可靠性研究阶段和现场故障分析阶段。

根据这种情况,可以想象,良好的DFT 策略应能够满足芯片调试的需要,而且,实际上也往往是如此。随着SoC(单片系统) 设计越来越复杂,一流

的设计团队表 示,他们将对支持调试而不是测试的电路提供更多的计划、实现工作以及芯片面积。

"十年前在设计3层金属层时,这并不是什么大问题,"Bay MICrosystems 工程部的高级副总裁Tony Chiang说。"如果芯片有问题,应该直接研究金属层来察看电路,而对于聚焦离子束系

统则应该重新布线。现在,对于9层金属层和0.2mm金属间距,问题就不是那么简单了。必须将电路设计成具有从芯片外部能控制和能观察的,而在成本和时间预算上不超出我们的目标。"

这种情况,简单扼要地描述了调试设计界的情况。

技术概览

调试与DFT并不是完全脱离的。Broadcom公司的测试开发工程高级总监Kris Hublitz举例介绍说,Broadcom有一个由70多名工程师组成的公司级团队,他们与公司其它的芯片设计团队共同从事调试和测试。Hublitz再三宣称DFT厂商LogicVision是Broadcom芯片调试策略的主要合作伙伴。

其他人也同意这种观点。"调试设计与生产测试并不是毫无关系," CSR (Cambridge Silicon Radio) 的副总裁David McCall说。"两者的起点差不多。"

很多设计经理强调,这一起点就是探寻电路的能控性和能观性。调试与生产测试相似,基本问题是将电路设置在一个已知的状态,然后开始运行,观察其行为。在中等规模的集成中,边界扫描技术可有效地完成此任务。由于芯片内部状态较少,可以全面地对其进行测试:将输入通过已知的一系列状态,对电路进行时钟同步,然后观察输出。

随着微处理器的出现,事情变得更加复杂了。微处理器有很多内部状态,所以只将输入施加给一个已知矢量并观察输出并不是特别有效。早期,业界尝试了多种技术使微处理器实现可调试,从对寄存器间的每群逻辑进行扫描到依赖同类的跟踪、断点及微机用于进行软件调试的单步函数等。将两种方法结合起来才能起作用。

如今设计人员对SoC的数字部分使用相同的工具套件。另有一些技术用于混合信号的模拟电路。但没有单独一种方法可以囊括整个复杂的SoC。所以,调试的设计流程包括将系统分割成独立的可调试模块,对每个模块实施一个调试策略,并将这些策略整合到一个完整芯片的方案中,使单个模块的用户接口相似并尽量减少电路需要的芯片资源。最后,设计师必须使用这些调试资源重新检查,使完全集成的芯片的运行既可控制又可观察,因为你不能只根据隔离功能模块就能判断某些问题。

数字SoC

最基本的SoC 形式是由简单的往往是可编程的外设模块和内存所包围的CPU 核。多数情况下,CPU 核为第三方的IP,至少有一个内部调试内核的选项。软件开发团队经常强调这一点。此内核与标准的DFT 电路相结合,这种电路是设计团队为外设所实施的,以实现能观性和能控性来隔离故障。可以在CPU 核中应用这种调试内核,模拟核的非同步部分,以捕捉结果。通过让CPU 读写外设寄存器,此内核也可模拟并观察外设,通常允许设计师在可以处理的级别上确定扫描链中的故障。

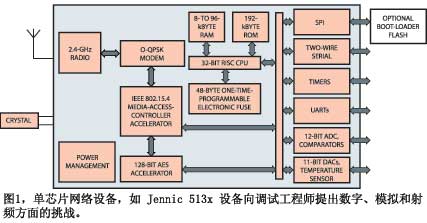

但如今并没有多少这么简单的SoC(图 1)。更多的情况下,芯片有几个或一群CPU 核和几种不同的处理器内核。某些外部控制器非常复杂,只用CPU对其进行模拟来观察结果,并不能对其有效诊断。还有多个时钟域,它们之间通常彼此并不同步。这样的芯片需要更有效的方法来调试。

而调试则完全不同了。调试的目的并不只是简单地确定芯片出现了故障,而是要找出故障的原因。这种检查并不限于在测试台上的几秒钟,可能要持续数周时间。它并不是自动进行的,而是需要芯片设计团队的参加。它出现在设计周期中的离散点上:在第一个芯片设计阶段、在可靠性研究阶段和现场故障分析阶段。

根据这种情况,可以想象,良好的DFT 策略应能够满足芯片调试的需要,而且,实际上也往往是如此。随着SoC(单片系统) 设计越来越复杂,一流

的设计团队表 示,他们将对支持调试而不是测试的电路提供更多的计划、实现工作以及芯片面积。

"十年前在设计3层金属层时,这并不是什么大问题,"Bay MICrosystems 工程部的高级副总裁Tony Chiang说。"如果芯片有问题,应该直接研究金属层来察看电路,而对于聚焦离子束系

统则应该重新布线。现在,对于9层金属层和0.2mm金属间距,问题就不是那么简单了。必须将电路设计成具有从芯片外部能控制和能观察的,而在成本和时间预算上不超出我们的目标。"

这种情况,简单扼要地描述了调试设计界的情况。

技术概览

调试与DFT并不是完全脱离的。Broadcom公司的测试开发工程高级总监Kris Hublitz举例介绍说,Broadcom有一个由70多名工程师组成的公司级团队,他们与公司其它的芯片设计团队共同从事调试和测试。Hublitz再三宣称DFT厂商LogicVision是Broadcom芯片调试策略的主要合作伙伴。

其他人也同意这种观点。"调试设计与生产测试并不是毫无关系," CSR (Cambridge Silicon Radio) 的副总裁David McCall说。"两者的起点差不多。"

很多设计经理强调,这一起点就是探寻电路的能控性和能观性。调试与生产测试相似,基本问题是将电路设置在一个已知的状态,然后开始运行,观察其行为。在中等规模的集成中,边界扫描技术可有效地完成此任务。由于芯片内部状态较少,可以全面地对其进行测试:将输入通过已知的一系列状态,对电路进行时钟同步,然后观察输出。

随着微处理器的出现,事情变得更加复杂了。微处理器有很多内部状态,所以只将输入施加给一个已知矢量并观察输出并不是特别有效。早期,业界尝试了多种技术使微处理器实现可调试,从对寄存器间的每群逻辑进行扫描到依赖同类的跟踪、断点及微机用于进行软件调试的单步函数等。将两种方法结合起来才能起作用。

如今设计人员对SoC的数字部分使用相同的工具套件。另有一些技术用于混合信号的模拟电路。但没有单独一种方法可以囊括整个复杂的SoC。所以,调试的设计流程包括将系统分割成独立的可调试模块,对每个模块实施一个调试策略,并将这些策略整合到一个完整芯片的方案中,使单个模块的用户接口相似并尽量减少电路需要的芯片资源。最后,设计师必须使用这些调试资源重新检查,使完全集成的芯片的运行既可控制又可观察,因为你不能只根据隔离功能模块就能判断某些问题。

数字SoC

最基本的SoC 形式是由简单的往往是可编程的外设模块和内存所包围的CPU 核。多数情况下,CPU 核为第三方的IP,至少有一个内部调试内核的选项。软件开发团队经常强调这一点。此内核与标准的DFT 电路相结合,这种电路是设计团队为外设所实施的,以实现能观性和能控性来隔离故障。可以在CPU 核中应用这种调试内核,模拟核的非同步部分,以捕捉结果。通过让CPU 读写外设寄存器,此内核也可模拟并观察外设,通常允许设计师在可以处理的级别上确定扫描链中的故障。

但如今并没有多少这么简单的SoC(图 1)。更多的情况下,芯片有几个或一群CPU 核和几种不同的处理器内核。某些外部控制器非常复杂,只用CPU对其进行模拟来观察结果,并不能对其有效诊断。还有多个时钟域,它们之间通常彼此并不同步。这样的芯片需要更有效的方法来调试。

在这种情况下,有几种策略可用。Broadcom的Hublitz介绍的一种简单方法是使所有主要功能模块的输入和输出可以访问芯片的针脚。这种方法需要大量的多路复用。在有大量I/O 和内存接口的设计中,在引入任何额外访问进行调试之前,芯片针脚数已经限定了,设计人员必须复用针脚进行调试访问。只将输入输出简单引出每个复杂模块,可能比将其在主CPU 核上执行更有用,设计师可能需要引

芯片 相关文章:

- Spansion突破闪存芯片尺寸限制,电荷捕获技术功不可没(11-07)

- 中芯国际和香港应科院合推双模UWB MAC ASIC专用芯片(03-23)

- 语音芯片APR9600及其在电话遥控系统中的应用(05-04)

- 功能趋向多样化的语音编译码芯片(05-10)

- 基于NXP UOCIII芯片的小尺寸液晶电视设计详解(05-16)

- 基于NXP UOCIII芯片的小尺寸液晶电视设计方案指导(05-13)