基于H.264的Exp-Golomb解码器ASIC设计

ITU-T(国际电信联盟)和MPEG(运动图像专家组)联合推出了新一代视频压缩标准H.264/MPEG一4-10 AVC。

它在DCT变换、熵编码、去块滤波等方面采用了一系列新技术,在相同的重建图像质量下比H.263和MPEG-4节约了50%的码率,在高码率应用中表现更加优越。同时,它具有良好的网络亲和性,对网络传输具有更好的支持。

但是,在获得优越性能的同时,H.264编码和解码的计算量和复杂度均有大幅度提升。H.264算法在编码端比H.263复杂3倍以上,在解码端复杂2倍左右。对于较高分辨率的视频源,单纯依靠软件方式实现H.264视频压缩算法,往往不能胜任,尤其难以进行实时解码。因此,采用硬件方式实现H.264视频压缩算法具有重要的意义。

本文的研究目标是设计H.264标准中的Exp-Golomb解码器,在对其算法进行深入探讨的基础上,提出了一种高效且低成本的ASIC实现方案。

Exp-Golomb编码原理及解码算法分析

在H.264基本规范中,除了残差变换系数采用CAVLC编码方式外,其它句法元素均使用Exp-Golomb编码。Exp-Golomb编码是一种有规则的变长编码方式,在各类视频编码标准中被广泛应用。Exp-Golomb编码基于符号的概率统计进行编码,用短码字来表示出现概率高的信息,用长码字来表示出现概率低的信息,码长与被编码数成指数对应关系,从而使总体平均码字最短。与定长编码方式相比,节省了大量存储空间。

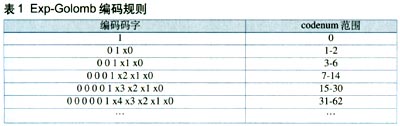

在H.264中采用的是0阶Exp-Golomb编码,编码规则如图1所示。

Exp-Golomb码字的逻辑结构为:[M zeros][1][INFO]。其中M个0和中间的1称为前缀,INFO是M位的信息值,因此,每个Exp-Golomb码字的长度都为2M+ 1。每个索引字codenum经过编码都可以对应一个如上结构的码字,它们之间的关系是:

codenum=2M+INFO-1 (1)

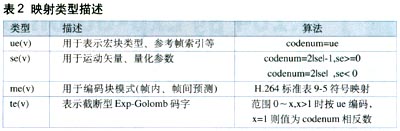

由式1可知,进行Exp-Golomb解码可先探测出码字前连续O的个数,再取出后缀,经该公式计算即可得到codenum值。在H.264中存在四种Exp-Golomb码:无符号型ue(v)、有符号型se(v)、映射型me(v)和截断型te(v)。因此,对于解出的codenum值,根据句法元素类型的不同有四种映射方式,如表2所示。根据相应描述完成映射后,输出syntax即为解码值。

Exp-Golomb解码器硬件结构设计

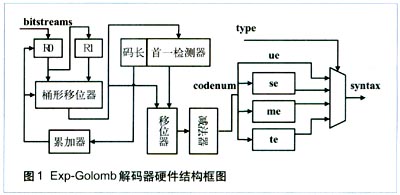

基于以上解码算法设计的Exp-Golomb解码器硬件结构如图1所示。整个系统主要由以下模块组成:输入码流缓冲移位模块、码长检测模块、 codenum生成模块以及句法元素映射模块。系统上电复位后,首先由码流缓冲移位模块提供待解码字,然后由码长检测模块中的首一检测器探测出连续0 的个数,即时计算得出当前码长送至累加器。同时,首一检测的结果和待解码字一起送至codenum计算模块,经移位、相减得到codenum值。最后将 codenum送至四个映射单元处理,最终解码句法元素由选择器输出至寄存器。整个解码流程用一个时钟周期完成。下文将详细叙述各功能子模块的硬件结构。

输入码流缓冲移位模块

输入码流缓冲移位模块是实现H.264实时解码的关键模块。由于在每个变长解码流程中,码长不可能事先确定,所以在解出码值的同时必须定位下一个码字。这就要求该模块具有快速响应和并行输出的特点。由于H.264中定义Exp-Golomb码最大码长不超过32,设计中采用两个32位寄存器,一个32位桶形移位器及一个累加器的组合来实现该功能,如图1左端所示。其中,寄存器Rn负责从外部模块读取数据,并和寄存器R1一起作为桶形移位器的输入; 在每个解码周期,桶形移位器移出已解码流的同时还要装载新的待解码流;而累加器则计数已处理码长,传送桶形移位器移位长度,判断并控制R0的读取和R1的更新。这样就为后续处理单元提供了连续不间断的码流。

码长检测模块

该模块的主要组成部件是一个16位的首一检测器,其功能是检测出输入序列中第一个1之前连续0的个数。码长(2M+1)的获取只需将首一检测的结果与一个1位进行位拼接即可实现,无需额外电路。另外,考虑到响应速度和路径延时,首一检测器的设计采用分组并行探测方式,其硬件结构如图2所示。输入的16位码流分成4组,每组4位均通过一个4输入与门,得到4位输出信号后送至优先编码器1,从而判断出首1所在区间。同时与门的四个输出还作为选择器MUX的控制信号,片选出存在首1的4位数据,并将其送至优先编码器2,判断出首1的具体位置。最后将两个编码器的输出进行位拼接即可得到首 1前连续O的个数M。

codenum计算模块和句法元素映射模块

codenum计算模块用于实现公式1的功能,设计中采用一个16位的桶形移位器结合一个16位减法器实现。桶形移位器根据首一检测结果,重新定位码流指针,正确输出码字中[1][INFO]部分,最后将[1][INFO]减去1即可得到codenum值。

关于句法元素映射模块,由于H.264中定义了四种:Exp-Golomb码,如前文表2所描述,存在四种不同的映射方式,本设计中采用四块组合映射逻辑加一个多选器实现,具体结构如图1右端所示。其中ue直接等于codenum,se与te的映射则分别采用包含二选一电路的简单组合逻辑实现,而me的实现较复杂,需查找H.264标准中定义的运动矢量、量化参数的映射表格,设计中采用ROM结构实现查表。

综合、仿真结果与性能分析

在上述硬件架构下,使用Verilog HDL进行Exp-Golomb解码器电路设计,并在Xilinx公司的ISE 8.2开发环境下进行了功能验证,选择Virtex 2系列的XC2V250器件。使用Synplify 7.7软件进行逻辑优化与综合,系统时钟频率可达104MHz。ISE完成布局布线后,通过ModelSim 5.8调用JM86生成的测试向量进行后仿真,最后与软件的计算结果相比较,验证了设计的正确性。

使用Synopsys公司的Design Compiler工具在0.18μm的SIMC CMOS工艺条件下,对RTL代码进行综合优化,时钟频率最高可以达到200MHz。通过设置不同的面积、时序及功耗约束条件,缩短关键路径的延时,综合出等效门数2276门、时钟频率为162MHz的最优设计。在此工作频率下,该Exp-Golomb硬件解码器电路解出一个句法元素只需耗用单个时钟周期,因此本设计可满足H.264高清晰度视频实时解码的要求。