视频监视领域的视频压缩与数据流

在DSP/GPP SoC系统中采用MJPEG 标准时,开发人员应首先适当拆分功能模块,以提高系统性能。

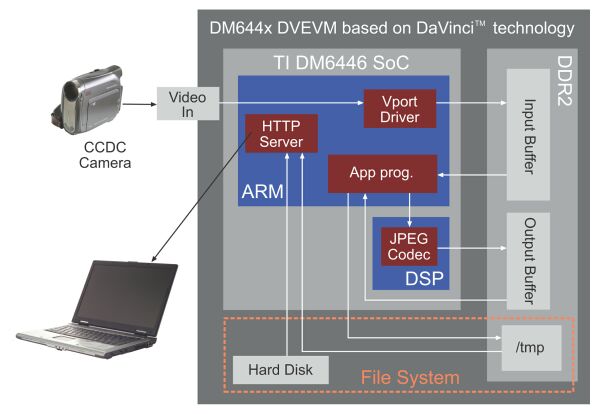

EMAC 驱动器、TCP/IP 网络栈和 HTTP 服务器协同工作,将压缩影像以流媒体形势输出。视频采集驱动器和 ATA 驱动器均应部署在 ARM 上,这样有助于减轻 DSP 的处理压力。而 JPEG 编码器应在部署在 DSP 的内核上,因为DSP VLIW 架构特别适用于这种计算强度大的工作。

一旦摄像头通过处理器上的视频输入端口采集到视频帧,原始影像就通过 JPEG 编码器压缩,随后将该压缩影像保存到设备硬盘上。

我们通常用 PC 监控实时视频场景,首先检索出视频服务器中的流媒体,然后进行解码,最后在显示器上显示视频影像。编码的 JPEG 影像文件可由设备通过因特网检索,因此我们不仅可在一台 PC 上同时监控多个视频流,而且通过因特网能够从多个点同时查看这些被检索到的视频流。VSIP 局端通过 TCP/IP 网络能与视频服务器相连,而且可位于网络中任何位置。这与传统模拟系统相比,是一个巨大的进步。就算出了问题,也只影响一个数字摄像头,而不会影响局端。我们也可动态配置 JPEG影像质量,以满足不同视频质量要求。

优化JPEG编码器

JPEG 编码器的三大功能模块中,DCT 与量化器的计算任务较重。我们也可以注意到,就这两种模块而言,高度优化的汇编代码和未优化的 C 代码之间存在很大的性能差异,因此有必要对这两个模块进行优化。

优化 2D 8x8 DCT功能模块有助于减少加、减、乘等运算次数,避免原始方程式的冗余计算。目前已推出了众多快速 DCT 算法,其中陈氏算法 (Chen’s algorithm) 广为业界采用。就 2D 8x8 DCT 而言,陈氏算法需要进行 448 次加减运算以及 224 次乘法运算。

加减法和乘法功能块可进一步拆分为多个功能单元(均部署在 DSP 内核上),以执行并行指令并提高性能。在开销忽略不计的条件下,高度优化的 DSP 汇编代码能在 100 个循环之内顺利完成 2D DCT 计算任务。其它快速 DCT 算法要求的计算量更少,不过往往会要求更多缓冲区来保存中间计算结果。就采用管线 VLIW 架构的新型 DSP 而言,存储器数据存取工作量比乘法运算工作量大,因此开发人员在优化算法时应考虑计算与存储器存取之间的平衡问题。

每个像素的量化过程均需要进行乘法及加法运算。这种计算结果通常只需要 16 位的精确度即可,而 DSP 寄存器则需要 32 位。优化量化器模块的最初想法是在单个寄存器中存储 2 个像素,然后对这两个像素执行加法及乘法运算;第二种方法就是并行使用多个 DSP 功能单元。由于 TMS320DM6446 中的 DSP 内核有 2 个乘法器和 2 个加法器,因此我们可同时量化高达 4 个像素。最后但不是不重要的一种做法就是充分利用管线 DSP 架构。DSP 内核在量化当前 4 个像素时,可从存储器读取下一组" 4 个像素",这样每个循环都能向乘法器和加法器提供数据。前两种方法由开发人员亲自编写优化的 C 代码或汇编代码即可实现。管线代码可采用 DSP 编译器。

除了优化每个功能模块之外,我们还可采用乒乓 (PING-PONG) 缓冲技术来优化系统级 JPEG 编码器。DSP 内核存取内部 RAM(IRAM) 中的数据的速度比存取外部 DDR2 存储器中数据的速度快得多。但 IRAM 容量有限,不能满足整个输入帧的要求,因此同一时间在 IRAM 中只能处理一部分模块。处理乒乓集时,DMA 将乒乓集从 DDR2 传递至 IRAM,这样 DSP内核就能在完成当前工作后立即开始处理下面的数据。

显然,视频监视系统的数字化已经全面展开。了解视频压缩、系统分区和编解码器优化等技术,对开发新一代视频监视系统以满足不断增长的需求来说至关重要。

作者:Zhengting He,德州仪器 (TI) 软件应用工程师

本文由TI供稿

家居安防 视频压缩 VSIP 视频监控 JPEG 相关文章:

- 家庭智能报警系统解决方案 (01-05)

- CPU单片机系统设计在社区安防系统中的应用 (07-28)

- H.264:视频压缩编码的新发展(08-28)

- H.264/AVC视频压缩编码标准的新进展(08-29)

- H.264/AVC技术进展及其务实发展策略思考(10-29)

- IPTV经典技术(08-15)