执同行业之牛耳,三星65nm 4Gb NAND闪存剖析

Insights尚没找到IM Flash和瑞萨科技推出的4Gb产品。IM Flash需提供有竞争力的产品来与位列前三甲的NAND制造商竞争。瑞萨正生产一款90nm的4Gb MLC NAND闪存,但该公司业已声明将不再进行更先进节点的研发。

技术升级挑战

在解决若干升级挑战之后,三星成功地将其闪存技术推进至65nm节点,这些挑战包括:单元对准、沟道氧化物厚度和闪存单元耦合。 现在,三星能集中精力用65nm节点实现MLC器件,以拓展其65nm产品线,并进行55nm节点的开发。为在成本敏感的应用中与东芝的70nm MLC器件竞争,三星需要开发MLC产品。

NAND市场的竞争肯定会更加激烈,制造商需要采用领先的工艺节点制造器件。三星、东芝和Hynix/ST全都处在70nm或更先进的水平,所以,这些制造商将很快转向65或55nm工艺技术。IM Flash只有快速挺进这些节点才能有竞争力。所以,三星不能高枕无忧,它必须快速扩张其产品线并进军55nm节点。

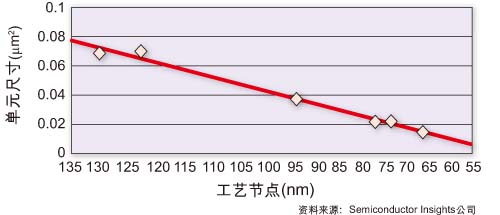

图2:采用55nm工艺的下一代NAND闪存的单元尺寸趋势预测

用55nm节点制造的器件正在开发中,预计于2006年底或2007年初投入生产。它们可能是来自三星、东芝或Hynix/ST的16Gb MLC器件。55nm节点器件的单元大小可能在0.0084μm2左右,最初的裸片大小在140到160μm2之间。这些预测是根据历史的裸片和单元尺寸演进导出的。55nm器件将与先前的65nm和70nm器件有某些共同特性,但需处理一些关键的缩微问题,包括单元对准、沟道氧化、多晶硅层间(interpoly)电介质、相临单元间的耦合(交叉干扰)和高压晶体管设计。

随着器件尺寸越来越小,对模层之间对齐的改进明显地是一个一直需要关注的问题。越小的器件需要的工作电压越低,这种情况又导致在将电荷送往或移开浮动栅时,需更薄的沟道电介质。但薄电介质并不那么可靠。在先进节点,影响单元晶体管浮动栅的活动区域范围更小,但控制与浮动栅的耦合比例需保持恒定。所以需要一种更薄的多晶硅层间电介质。在两种电介质的情况下,高k(介电常数)材料能降低有效电厚度,且同时能够以更宽的物理厚度维持更高的可靠性。

但新材料的引入,将带来新的挑战。将单元封装得越紧,当对一个浮动栅充电时,对相临存储器单元工作产生影响的风险就越大。最终,闪存操作依靠相对高的电压对单元进行编程和擦除。用于切换这些电压的控制晶体管需尽可能保持较小,以便在给定的硅片面积内它们不会降低存储器单元的效率。

三星在市场上率先推出65nm存储器件--K9F4G08U0A。它进一步证明,三星继续致力于用先进工艺节点进行生产,以期在与其它存储器厂商竞争中占有优势。但在成本竞争激烈的存储器市场,仅在工艺节点方面占先是不够的,另外,为在对成本敏感的存储器应用中竞争,还需要诸如MLC编程等电路技术。

现在,三星有了一款能工作的65nm器件,它可能致力于通过增加MLC产品等手段丰富其65nm产品线,并将工艺节点推向55nm。

作者:Geoff MacGillivray

内存分析师

Semiconductor Insights公司

NAND闪存 相关文章:

- 原子vs电子:闪存与磁盘的区别(02-07)