对存储带宽的要求使手机设计面临两难抉择

如何在增加存储带宽以适应各种新兴应用需要的同时又将尺寸降至最小和将成本降至最低,这是横亘在手机制造商面前的一道难题。面向视频、音乐、导航和联网等多种应用的最新功能型手机要求高达数千兆位(Gb)的存储带宽,这比现今已有的手机高出一大截。因此,需要一种更好的存储器控制器接口,以此支持未来手机的需求。

举例来说,一个分辨率为1,280×1,024、刷新频率为60Hz的24位(RGB)彩色编码LCD就需要1.5Gbps的存储器缓冲器读/写总带宽,而总的存储器带宽则高达3.7Gbps。该带宽用来驱动外置显示器的常规分辨率,但渲染及其它功能则不在其内。将手机显示器与目前计算机的图形系统相比较并不过分,因为移动电话也和计算机一样集成了千兆赫兹(GHz)的处理器和DDR DRAM主存储器。这些系统都需要80至400Gbps的存储器带宽。

在一款集成了两个处理器内核(一个用于基带处理,另一个用于应用程序处理)的典型高端手机中,两个处理器均需要以非易失性(Flash)存储器来存放代码,以易失性存储器(SRAM和DRAM)作为处理数据时的临时缓存器。

当应用程序处理器执行用户可载入的多媒体应用程序时,需要大量快速存取存储器。然而,这种速度需求超过了现有最快闪存的存取速度的数倍。为实现这类性能,可以用价格较为低廉的NAND或MirrorBit ORNAND闪存来存放应用代码,然后将其复制到更快的DARM中来执行。因此,应用程序处理器一般需要NAND或ORNAND和DRAM存储器。

相对而言,基带处理器要执行深层的嵌入协议堆栈。这类代码最理想的是闪存直接执行(即片内直接执行,或缩写为XIP),并且需要对闪存进行随机存取。只有NOR闪存支持高效的XIP模式,故通常选择NOR存储器来存放基带代码。DRAM能够作为基带处理的临时缓冲器被应用程序处理器共享,或者是NOR存储器可与专用于支持基带处理的SRAM或pSARM结合使用。

集成如此多种类的存储器通常需要超过100个引脚专门作为存储器接口,而这一数量占据了整个手机CPU引脚总数的大约30%。德州仪器的OMAP 1611和意法半导体的Nomadik宏架构就是含有大量连接存储器的引脚的高性能CPU的代表。

而随着用户对诸如LAN连接、GPS功能和移动电视(TV-on-mobile)等新型手机功能的需求,OEM们面临着更大的挑战。上述性能需要更强的处理能力,进而需要更大的内存带宽来支持这种处理能力。这就意味着必须增加引脚的数量以支持增强的数据处理能力。目前的系统内存已占用了整个CPU很大一部分引脚数量,若要再增加引脚就会带来种种问题和技术挑战:

* 每个引脚都会为手机CPU直接增加0.4美分的成本,进而导致信号和相关电源/地引脚的总体成本提高60美分。

* 减少引脚数量可以缩小封装体积、降低其成本。

* 对于焊盘有限的设计而言,I/O数量的减少可直接降低裸片成本。

* 采用大量引脚的CPU需要更多层的电路板用于信号走线,这样将增加系统的成本。

* 通过通孔连接多层板的布线方式会引起噪声问题。

* 为容纳更多的引脚就需要更大的面积,但这样做又与手机小型化、超薄化的趋势背道而驰。

单纯地暂不集成这些先进功能,而是等待开发出更快速的存储器解决方案,这种做法显然并非上策。虽然扩展存储器总线接口在技术上具有可能性,但由于增加了CPU上业已庞大的引脚数目,这种方法并不合理。因而存储器总线必须向着有利于DRAM性能的方向发展,同时寻找能够支持频率变化并减少引脚数量的新的I/O技术。考虑到围绕存储器系统而构建的众多基础架构,想要从根本上改变内存总线是相当困难的。

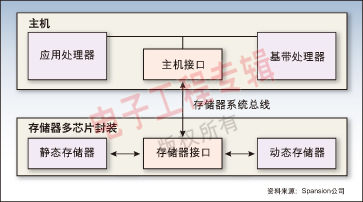

图1: 存储器件可以共享客户端和主机之间的总线

图2: 存储控制器接口链接系统总线和存储器件

解决方案概述

存储器控制器包含了两个接口。主机接口将控制器与系统总线相连,存储器接口则将控制器与存储器件相连。两个接口分别工作在各自的时钟域中,并通常具有独立的先入先出(FIFO)队列。这就使得存储器控制器可以通过以高速、少引脚数量的总线来替换队列,从而很容易地重新分区为主机接口和存储器接口。

以这种方式对存储器系统进行重新分配,为主机和存储器系统之间提供了一条统一总线,同时考虑到了密度、存储器类型以及速度级等性能指标。此外,该方法还最小化了外部总线的负荷,因而允许更高的总线频率,这是减少引脚数量的预备条件。而且,重新分区也同时把存储器件之间大量引脚的接口限制为典型多芯片封装(MCP)内部的一种解决方案,这降低了手机成本,并允许在MCP中容纳更多的存储模块(Memory Bank)。

主机与存储

- DSP片外高速海置SDRAM存储系统设计(10-02)

- 选择低成本FPGA硬件和IP方案加速高清平板电视设计(03-23)

- 汽车中的软件无线电(07-07)

- AVS编码与DSP实现的视频编码器(08-02)

- 基于ARM的嵌入式最小系统研究(03-27)

- 全面解读 嵌入式DSP上的视频编解码(08-19)