Virtex-5 FPGA致力更高系统性能

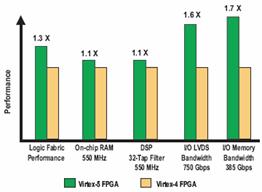

客户设计基准 图3:根据利用ISE 8.2i软件实现的一套74个客户设计的比较 图4:Virtex-5 FPGA性能的改进

为了进一步评估由Virtex-5 FPGA逻辑构造所提供的性能改进,我们利用赛灵思的ISE软件实现了一组客户设计。

这些设计完全采用VHDL或Verilog编写。我们利用库组件或综合参考的直接调用方法实现了一些像存储器和FIFO那样的特殊设计单元,但是许多是利用由CORE Generator™软件生成的EDIF模块实现的。

对于这些基准,我们采用Synplicity公司的Synplify Pro工具以时序驱动方式执行综合,并利用严紧和现实的约束来有效地测量性能。完成这一点就确保所有特殊优化和逻辑复制获得了使用。

在ISE软件中的实现是把布局和路由努力设置到"high"来完成的。时钟被以5%的增量反复增加,直到该设计不能满足设计约束。

结果是-与利用Virtex-4 FPGA实现的设计相比-平均性能提高了30%,如图3所示。

在展示适度改进的设计中,要么具有较少的逻辑级,要么为使用硬IP模块或改进性能的进位链结构提供很少的机会。

图4通过把Virtex-5 FPGA对前一代Virtex-4 FPGA的性能改进进行分类做了总结。

利用其新的ExpressFabric技术和对其它高性能硬IP及I/O的紧密耦合,与前一代架构相比,Virtex-5 FPGA家族表现了重大的性能提升。

FPGA DRAM DSP DDR RAM ROM 相关文章:

- 利用FPGA和新技术,使LCD进入HDTV市场(08-27)

- 基于DSP和FPGA的电视观瞄系统设计(09-02)

- FPGA与SRAM相结合完成大容量数据存储(09-03)

- HDTV接收机中Viterbi译码器的FPGA实现(09-09)

- 基于FPGA的液晶显示接口设计 (09-26)

- 解决硬盘驱动器能耗难题(10-13)