技术分析:动态功耗调节详解

大而增大的动态电流。如果输入频率足够低,影响微乎其微。随着频率增大,放大器输出端的RC网络会显示更大的负载,因而需要放大器提供更大的电流来处理此信号。

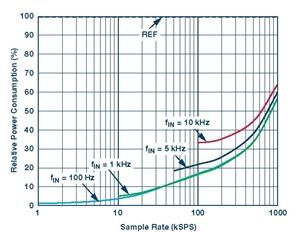

使用前面提及的ADA4805-1和AD7980并将这些概念综合在一起便可得到图4中的曲线。此图显示了进行动态功耗调节的ADC驱动器放大器相对于同样的放大器在一直启用时的功耗(用百分比表示)。我们绘制了选定输入频率下的DPS效率图,用以描述更高的输入频率对功耗的影响。我们确定了介于1 kSPS至1 MSPS之间的多个采样速率的最小tON,并将其定义为导致SINAD(信噪失真比)与一直启用的放大器相比减小不超过0.5 dB的tON。此图显示,在低采样速率下处理缓慢输入信号时,功耗节省量最高可达95%。但对更高吞吐量的系统而言更重要的是,潜在功耗节省量仍然非常高,在100 kSPS时最高可达65%,在1 MSPS时最高可达35%。必须注意,图4反映的是一个单位增益缓冲器在持续被采样的系统中的性能。但是,如之前所述,可将这些DPS概念轻松运用至基准电压源缓冲器,而且得到的结果类似。

图4.放大器功耗与动态功耗调节的关系-试验结果

虽然DPS是一种相对较新的概念,而且需要考虑设计和时序因素,但是其初步成果非常有效。很明显,对更高性能和更低功耗的渴望将延续到未来,从而进一步增加对创意低功耗解决方案的需求。

作者简介

Bruce Petipas是ADI公司线性产品和技术部门的一位应用工程师。他从马萨诸塞大学获得电气工程学士学位后,于1999年加入ADI公司。在此期间,Bruce专攻高电流放大器的各个领域,最近,他开始致力于ADC驱动应用。

在线支持社区

访问ADI在线支持社区,与ADI技术专家互动。提出您的棘手设计问题、浏览常见问题解答,或参与讨论。

ez.analog.com