片上网络技术发展现状及趋势浅析

工艺条件下高集成度芯片发展的必然需求。

NoC设计空间

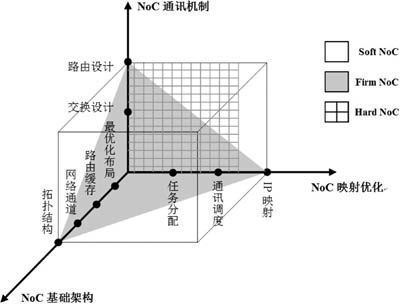

完整的NoC设计方法学包括很多方面的问题,它们对NoC的发展都是至关重要的,且已经引起了学术界的广泛研究。Carnegie Mellon大学的U.Y. Ogras等人在文献[4]中提出了NoC设计空间的概念并将NoC研究归纳为三大类关键问题:基础架构、通讯机制和映射优化,如图2所示。

图2 NoC设计空间示意图

图中,"Hard NoC"(网格部分)指基本架构确定,各PE节点的内容也固定的一类NoC结构,其设计空间只是图中一矩形部分,设计余度最小;"Firm NoC"(灰色阴影空间)指其基本架构已确定,网络通道宽度与通讯节点缓存大小不确定,其他维度对设计者完全自由的一类NoC结构,设计者可以根据确定的应用实现最优的布图规划、通讯调度与任务分配算法、IP映射算法和路由交换解决方案,设计空间比较灵活;"Soft NoC"(白色立方体部分)指设计者需要根据应用来优化NoC设计空间的所有问题,设计灵活性最高,但设计难度和工作量也相应最大。

设计者根据给定的具体应用,依据应用特征图(Application Characterization Graph,APCG),在时间、成本、技术储备等约束条件下,首先按应用选择基于哪类NoC开展设计;其次在该类NoC的设计空间范围内解决相应关键问题,以探索最优的NoC实现方案。

NoC关键技术难点

NoC关键技术主要包括系统建模、拓扑结构、路由方法、交换方法、缓存策略、服务质量和映射优化等,近年来都不同程度地取得研究进展,而阻碍NoC走向大规模应用的瓶颈在于以下几方面:

存储结构问题

Memory是NoC中十分重要的组件,在现有的片上多处理器系统中,存储器占到70%的芯片面积,并且在不久的将来会上升到90%[5];而从能耗的角度来看,存储器所引入的功耗也可达系统功耗的90%[6],这对芯片的散热、封装和可靠性等都带来了严重的问题;NoC系统需要大量的存储元件,并被组织成复杂的存储子系统(memory subsystem),这个存储子系统将支持NoC的并行数据存储、传输及交换。NoC中大量的存储资源必将占用多个路由节点,且由于处理单元与存储资源之间的数据交换非常频繁,若在数据包传输路径上路由节点数目过多,会带来很大的通信延时。如何有效缩短源节点到目的节点间的距离对提高整个NoC系统性能十分关键。

再者,从通信带宽的角度,随着工艺的进步,计算访存比进一步增大,意味着基于该结构获得接近峰值性能的应用算法越少。这就引入了一系列问题,如何让众多处理器核有足够的数据可算?如何更充分地利用片上有限存储空间实现核间共享,以避免片外访存?如何充分利用有限访存带宽,尽量让访存通道优先满足处于关键路径处理器核的访问请求?最近美国Sandia国家实验室提出在多核处理器芯片上堆叠存储芯片,来解决带宽增长不足的问题,这或许是一种可行的方案。

总而言之,片上存储结构已经成为影响NoC性能的关键因素之一。

软件并行化问题

未来的基于多核的高性能处理芯片可能会遇到很多传统的串行程序自动并行化方法较难实施的应用。如果不能有效地利用NoC片上并行处理资源,则并行计算的实际性能将会很低,因此如何通过有效的方法和模型,充分地利用NoC的众多处理单元,并极大地降低应用的开发难度,便成为迫切需要解决的问题。

与并行计算机发展过程中遇到的问题相类似,NoC并行处理体系结构所面临的主要问题是如何将应用中蕴含的不同层次、不同粒度的并行性有效地提取出来并映射到多核的并行硬件结构上去。这一问题的解决涉及包括程序设计模型、程序设计语言、编译系统及硬件支撑等在内的多个方面。

总体来说,开发并行程序可以有三种途径,一是串行程序自动并行化。这条路目前尚未走通,更为实际的目标应为人机交互的自动并行化;二是设计全新的并行程序设计语言。这种方法的缺点是需要全部改写原有程序,对用户来说成本和风险也很高,且效率不能保证。但是,随着多核的出现,若面向大众推广并行计算环境,就必须有一种新的容易被接受的程序设计语言。目前国际上正在研究的新兴并行程序设计语言如IBM的X10、UPC(统一并行 C语言,C语言的扩展)和Titanmin(Java的扩展)等;第三条途径就是串行语言加并行库或伪注释制导语句的扩展,也即增加一个库或一些新的制导语句来帮助进行消息传递和并行。这正是MPI和OpenMP所采取的途径,也是目前比较容易被接受且性能较高的途径。但其程序开发效率很低,难度也比较大[7]。

功耗管理问题

虽然NoC有助于提高芯片的能效(Energy-Efficiency),但不能忽视,由于多核系统片上集成规模的大幅度增加,功耗问题依然突出

- 安森美推出应用于高速联网和自动测试设备的新器件(03-11)

- ST推出高集成度的多路输出稳压器PM6641(04-11)

- ST推出STC03DE220HV ESBT功率开关(04-25)

- 意法半导体推出首款采用65nm制造工艺的SPEAr定制芯片(05-02)

- ST发布STC03DE220HV ESBT功率开关,提高ESBT额定电压(04-27)

- ST推出全新快速恢复MOSFET产品(04-28)