基带处理芯片共享高速存储器模块设计

假设CPU0写数据到用户RAM,接着CPU1从用户RAM读数据。这种情况下,CPU0首先写数据,然后将标志变量置1,表示用户RAM内的数据已更新。标志变量地址位于用户RAM地址范围内。接着CPU1读标志变量,若变量为1,则从用户RAM内对应地址读取CPU0写入的数据,并将标志变量置0;若标志变量为0,则表示用户RAM内数据已被CPU1读取过。

使用以上方法可实现核间数据交互。由于同一时刻AHB总线上只能有一个设备利用总线进行读写,所以可以保证读写操作的原子性,即标志变量不可能被CPU0和CPU1同时访问。从而保证了标志变量的有效性。

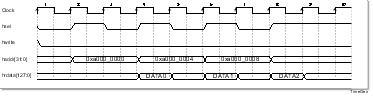

图 2?2 用户RAM读时序

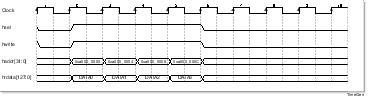

图 2?3 用户RAM写时序

参 考 文 献

[1 ]John L . Hennessy , David A. Patterson , Computer Architecture : A Quantitative Approach , Fourth Edition [ M ]. Ap professional ,1990

[2 ] Sun Microsystems Inc. OpenSPARC T1 Microarchitecture Specification[ R]. 2006

[3 ]David A. Patterson , John L . Hennessy , Computer organization and design[ M ]. Morgan Kaufmann ,2004

[4 ] Michael D. Ciletti , Advanced digital design with the Verilog HDL [ M ]. Pearson ,2005

[5 ]周立. 计算机系统结构 [ M ]. 北京 :清华大学出版 社 ,2006

- 单节锂离子电池保护芯片的设计(11-04)

- 基于手写辨识芯片的汉字手写输入技术(11-03)

- 单芯片指纹锁设计方案(03-24)

- 基于SystemC的系统级芯片设计方法研究(05-16)

- 单芯片嵌入式网关在煤矿井下人员定位中的应用(06-23)

- Broadcom推出高清卫星机顶盒单芯片系统解决方案(08-16)