基于异构多核全高清H264解码系统设计

PEG2、H263等常见的视频编解码标准。为了释放CPU,让其更有效的进行数据准备和逻辑功能控制,IVA-HD集成了7个硬件加速引擎,他们和H264解码各个功能模块所对应关系在图3中用虚线框表示,其中加速引擎名称core1-5所对应的模块功能分别是:熵解码、反量化和反变换、环路滤波、帧内预测、运动补偿。

2系统设计

全高清H264解码任务由主处理器Cortex-A9和协助处理器Cortex-M3共同完成,Cortex-A9主要负责从多媒体文件中或网络数据流中进行数据的读取、多媒体数据包过滤分离视频流和音频流、构建RPMsg控制消息进过virtio缓存封装发送给协处理核Cortex-M3以设置IVA-HD加速引擎的控制参数、向协处理器发送多媒体数据包进行H264解码、在协处理器完成解码任务后接收图像并通过DRM API及KMS模块绘制到屏幕上。

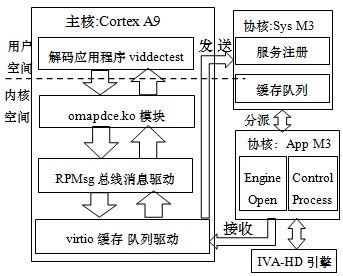

平台上有两个Cortex-M3处理核,分为Sys M3和App M3,都运行TI BIOS实时操作系统,其中Sys M3主要负责创建与Cortex-A9通信的virtio缓存队列,对程序执行流程和CPU负载情况进行记录,接收A9发过来的缓存数据并进行参数解析,同时根据缓存中dst参数分派缓存到App M3的相应消息链表中。而App M3协处理器则完成实际的解码工作,App M3将通过运用于嵌入式平台的Codec Engine来完成对IVA-HD加速引擎的操作。App M3将提取消息链表中消息请求相应设置IVA-HD加速引擎的状态和初始化参数,在进行实际解码时会通过Codec Engine来调用IVA-HD加速引擎来完成解码任务并将解码结果通过缓存队列发送回Cortex-A9处理器。整个系统解码的框架图如图4所示:

图4 H264解码器工作框架图

3系统实现

3.1 Cortex-A9软件实现

Cortex-A9运行Linux操作系统,包括内核模块omapdce.ko和virtio缓存、RPMsg总线驱动程序设计和ffmpeg多媒体库及DRM显示接口调用。

3.1.1 virtio缓存队列实现

Virtio缓存队列以共享散列表的方式和协处理器进行数据通信,通过中断方式通知对方散列表的添加,包括以下几个方面:

1)Irq_require()注册中断函数,Register_bus_type("virtio")向系统注册virtio总线

2)Regsiter_virtio_driver(

3)系统在发现协处理器后将通过register_virtio_device(

4)virtio_bus->match(

3.1.2 RPMsg消息框架实现

RPMsg总线将挂载许多rpmsg_driver和rpmsg_device,和rpmsg_driver都有本地端口src和目的端口dst属性,每次发送消息时会调用rpmsg_send((void*)data,src,dst)将消息添加到virtio的缓存队列中,而当消息msg达到RPMsg总线时,总线把msg分配给dst属性和msg->dst相同的rpmsg_driver,并调用rpmsg_driver->callback()进行消息处理。

3.1.3 omapdce.ko驱动模块的实现

Omapdce.ko模块将作为一个RPMsg driver,其实现了应用程序引擎相关API的内核实现,主要包括ioctl_engine_open()、ioctl_viddec_create(),ioctl_viddec_control()、ioctl_viddec_process(),他们提供了应用API engine_open、viddec_create()、viddec_control()、viddec_process()的驱动实现,这些驱动函数将调用RPMsg总线rpmsg_send()、rpmsg_recv()与协处理器进行消息通信以完成工作任务。

3.1.4解码应用viddectest实现

H264解码应用程序viddectest的工作主要分为以下几个方面

1)Linux显示接口DRM初始化,通过Drmopen()函数打开/dev/dri/card0设备文件,获取设备资源drmModeGetResources(),创建帧缓存drmModeAddFB2()及设置输出分辨率及模式drmModeSetCrtc()

2)FFmpeg媒体库的调用,通过AVOpenStreamFile()打开多媒体文件,AVFindStream()分离出音频流和视流,然后依次通过AVGetPacket()读取视频流数据包送去解码器进行解码。

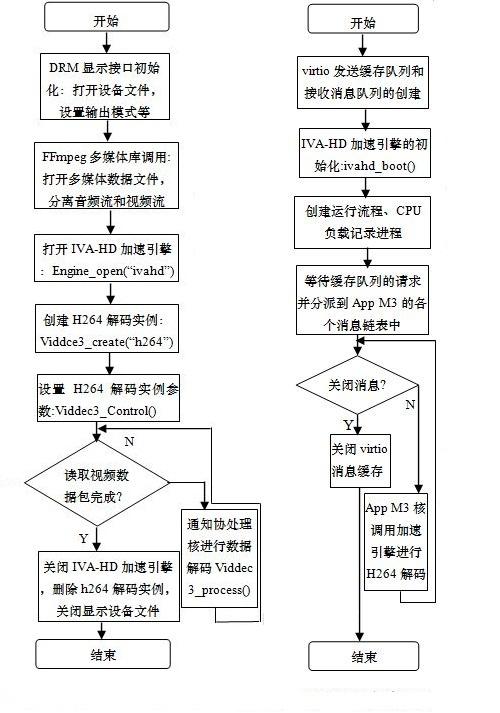

3)加速引擎初始化和利用消息总线进行解码数据通信,通过Engine_open()打开H264解码引擎,Viddec3_create()创建一个解码实例对象,Viddec3_control()设置解码所需的参数,Viddec3_process()将用RPMsg消息总线送出解码数据流并接收解码后的图像缓存数据,其流程图如图5所示:

图5&6 应用viddectest流程图&M3运行流程图

3.2 Cortex-M3软件实现

双核Cortex-M3运行TI BIOS实时操作系统,负责与主处理核的virtio缓存队列通信及通过codec engine调用IVA-HD加速引擎实现H264解码,运行流程图如图6所示,主要包括以下内容:

1) virqueue_create( virtio发送及接收缓存队列。

2) Message_get_queue( M3的消息队列中。

3) App M3将获取消息链表的消息,设置IVA-HD加速引擎的工作状态并初始化,如果为解码消息则通过Codec Engine调用IVA-HD加速引擎来完成解码过程。

4)将解码后的图像缓存封装成virtio缓存,调用Message_send_queue()通过virtio缓存队列发送回主处理核A9调用DRM进行显示输出。

- 音响系统的USB接口开发分析及主流芯片比较 (02-01)

- AVR全新32位微控制器实现真正的单芯片DRM数字音频编解码器(01-25)

- 便携式BD播放机系统的设计(05-24)

- 基于单片机AT89C51SND1C的MP3方案设计(07-24)

- 基于Atmega16的FEC设计与实现(07-15)

- 基于ARM的MP3播放器(10-17)