基于SOA架构的网络硬盘控制器的设计

表5-1 硬盘接口信号

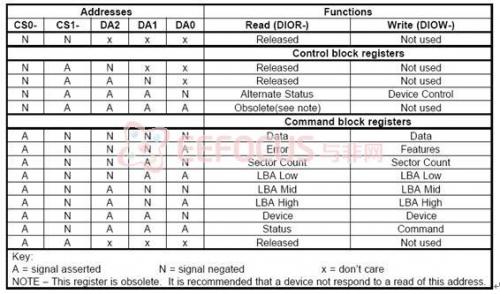

5.2 硬盘接口寄存器

主机对硬盘的访问是通过对接口寄存器的访问来实现的。ATA-6标准规定的硬盘接口寄存器如表5-2所示。这些寄存器按照功能划分为命令寄存器(Command block registers)和控制寄存器(Control block registers)。命令寄存器用来接收主机发出的各种命令和传送数据,包括数据寄存器、扇区计数寄存器等。控制寄存器用作控制硬盘操作,如使能硬盘中断、选择硬盘等。

表5-2 硬盘端接口寄存器

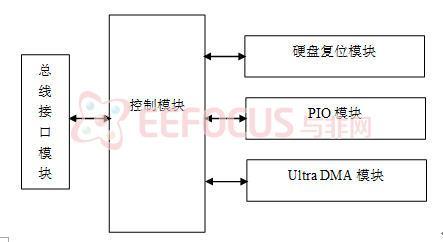

5.3 硬盘控制器模块设计

硬盘控制器模块内部结构如图5-1所示。

图5-1 硬盘控制器模块内部结构

5.3.1 总线接口模块

总线接口模块是硬盘控制器与PLB总线的连接模块,接收处理器通过PLB总线发来的操作命令及读写数据。

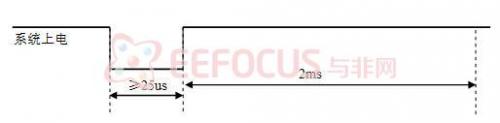

5.3.2 硬盘复位模块

硬盘上电后需要完成一个复位过程,即ATA/ATAPI-6标准中描述的上电及硬件复位协议。复位过程既可以通过软件编程实现也可以通过在硬盘控制器内部设计专用的逻辑来实现。系统上电后,硬盘控制器通过硬盘复位模块生成一个宽带大于25us的低电平复位信号,复位信号回到高电平2ms后,即复位操作完成。复位信号波形如图5-2所示。

图5-2 复位信号波形

5.3.3 PIO模块

该模块的功能是产生读写硬盘内部寄存器的时序,该模块产生待访问的硬盘寄存器的地址线,并输出读写信号,根据数据传输方向,发送数据到数据线或从数据线上读取数据,操作完成后,释放地址、数据线。

根据PIO读写时序,该模块应实现以下功能:

产生访问硬盘寄存器的地址信号,并具有一定有效宽带。 产生相应的读写信号DIOR-/DIOW-,当为写操作时,使数据具有规定的建立和保持时间;当为读操作时,给出读数据的时机。 处理硬盘输入的IORDY信号,当IORDY无效时,应延长对硬盘的读写周期。5.3.4 Ultra DMA模块

Ultra DMA模块是硬盘控制器的关键模块,其主要功能是实现Ultra DMA突发数据输出时序的控制。Ultra DMA操作可分为三个阶段,分别是初始阶段、数据传输阶段、传输中止阶段。

初始阶段的时序描述为:当硬盘发出DMA请求信号DMARQ,控制器通过DMACK-进行应答,等到硬盘发出的DDMARDY-信号有效后,控制器开始输出HSTROBE信号。

数据传输阶段的时序描述为:HSTROBE时钟的上升沿和下降沿都触发数据输出,在数据传输过程中,控制器可通过停止产生HSTROBE信号来暂停数据的输出,硬盘可以通过使DDMARDY-信号无效来暂停数据的接收。

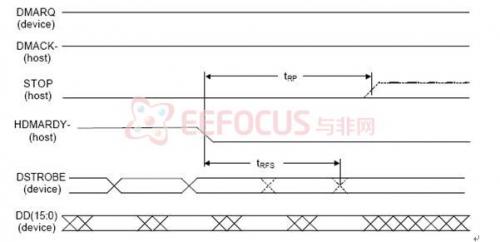

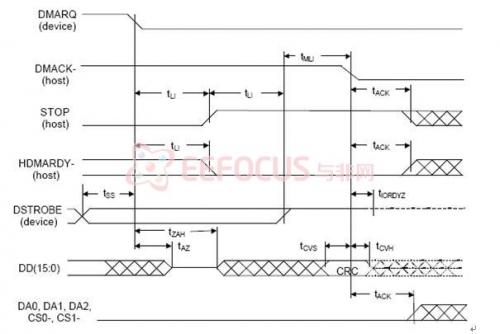

传输终止阶段,控制器和硬盘都可终止数据传输,终止数据传输可分为四个过程:停止请求、停止检查、HSTROBE返回高电平、发送CRC校验值。对于控制器停止数据传输,首先停止产生HSTROBE时钟信号,发出STOP命令信号,控制器检查硬盘的DDMARDY和DMARQ均无效后,使HSTROBE返回高电平,使DMACK-无效,并在DMACK-信号跳变沿处输出CRC校验值到数据线DD(15:0),如图5-3所示。对于硬盘停止数据传输,通过使DDMARDY和DMARQ均无效来停止数据传输,控制器需要在tL1时间内发出STOP信号,使HSTROBE返回高电平,使DMACK-无效,并输出CRC校验值至DD(15:0),如图5-4所示。

图5-3 控制器终止Ultra DMA数据传输时序

图5-4 硬盘终止Ultra DMA数据传输时序

5.3.5 控制器模块

控制模块是硬盘控制器的核心,该模块的主要功能是实现CPU对硬盘控制器中寄存器的配置,并根据相关寄存器的写入信息实现对应的控制操作。

6 总结

项目设计一种基于"流程+引擎+构件"SOA三层架构的网络硬盘控制器。采用FPGA作为系统控制器,在MicroBlaze软核处理器上移植PetaLinux操作系统,加载NFS网络文件系统,将扩展Int 13H规范中定

- ARM硬件设计三:JTAG引脚和PIO引脚(02-27)

- 高带宽嵌入式应用中SoC微控制器的新型总线设计 (02-02)

- 新型以太网控制器ENC28J60及其接口技术(06-23)

- 基于红外超声光电编码器的室内移动小车定位系统(06-30)

- 嵌入式指纹锁的设计与实现(07-13)

- 基于ARM控制器LPC2294的CAN/PCI智能通信卡设计(07-20)