基于DSP和FPGA的红外信息数据处理系统

现代空战中,光电对抗装备在战争中扮演着重要的角色,而红外侦测与跟踪系统由于采用的无源探测技术,因此与雷达等主动探测系统相比具有隐身性强、抗干扰能力好和小型化程度高等优点,受到业内的关注。新一代红外成像导引系统须具备高精度、处理速度快、实时性强且反应时间短等特点,这便要求图像处理计算机能满足图像处理中大数据量、复杂运算、实时性强、高传输率和稳定可靠等要求。文中从工作原理、硬件及软件3个方面介绍了基于DSP和FPGA芯片的红外信息数据处理系统设计方法。

1红外制导控制系统硬件总体设计

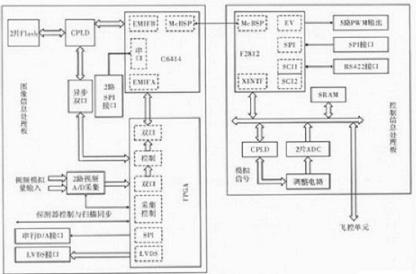

红外信息数据处理系统按照功能划分为两大板块,由图像信息处理板和控制信息处理板组成数据处理系统。其红外制导控制信息数据处理系统如图1所示。图像信息处理板主要承担大量的实时图像信号预处理、图像信号处理与控制任务;控制信息处理板控制接口信号的采集,跟踪回路的解算,控制输出及与飞控计算机等的通讯,同时控制管理模块也是系统的管理模块,完成对系统的输入/输出操作、同步控制、系统状态管理等功能。

图1 红外信息数据处理系统框图

2图像处理模块的硬件设计

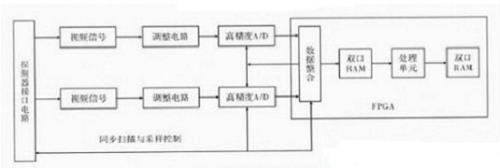

图像处理模块的硬件由复位电路、时钟电路、图像采集及预处理电路、DSP图像处理电路、电源转换电路和外部接口等电路组成。组成框图如图2所示。

图2 图像采集单元电路组成

2.1图像采集单元

图像采集单元包括扫描同步接口电路、探测器接口电路、前端调整电路、A/D转换电路、采样控制与数据整合电路及数据缓存(同步双口)电路等组成。电路组成框图如图2所示。扫描同步信号是来自系统中扫描模块,该信号提供系统时序基准,其信号同步于帧同步信号。扫描同步信号从底板连接器接入。探测器接口电路包括:参考电源、温度信号、采样控制信号及2路视频模拟信号等,以上信号在FPGA内部采集电路的控制下,保证每帧图像数据的同步采集。调整电路将探测器输出的视频信号调整至高速A/D输入的范围,差分视频信号经差分驱动器放大驱动,其共模输入电压为视频A/D片内参考信号(2.5 V)。模拟信号输入到A/D采用差分输入方式。视频A/D主要用于将视频电路间的模拟信号与数字信号进行转换。根据电路整体要求,A/D转换电路需满足采样频率高、功耗低、转换精度高等要求。采样控制和数据缓存电路由FPGA内部采样控制电路完成。数据缓存电路由FPGA内部双口存储器完成,具有高速、可同步及异步读写操作等性能。

2.2 DSP图像处理电路

DSP图像处理电路主要包括处理器及外围配置电路、存储器电路及与控制板接口通信的McBSP串口电路等。处理器选用TI公司高性能定点TMS320C641x系列中C6414 GIZA-6E3作为图像信息处理C6414-6E3,时钟周期为1.67 ns,内部工作时钟可达600 MHz,最高处理速度可达4 800 MIPS;内部存储器容量8 Mbit;有2个扩展存储器接口,EMIFA为64 bit,EMIFB为16 bit,EMIFA的总线频率可达133 MHz,最大可寻址空间为1280 MB;内核工作电压为1.4 V,工作温度可达-40~105℃。其完成红外成像制导导引头图像组合、分割与增强、模板匹配、背景处理、目标提取和目标跟踪等主处理算法。

FPGA预处理单元是图像信息处理板上另一个核心部件,采用Xilinx公司Vertex-II系列中的XC2V2000-FG676来实现。XC2V2000具有200万门的规模,内部的存储资源有1 Mbit的Select RAM,336 kbit的Distributed RAM,IO管脚资源达到408个,8个DCM.FPGA预处理单元设计由视频采集控制与数据整合单元、视频采集缓冲和主处理缓冲双口存储器、预处理单元、图像输出子卡数据传输接口控制、串行SPI接口控制器、LVDS数字视频输出接口、访问DSP/HPI接口的主机控制电路等部分组成。另外,图像信息处理板的FPGA配置可实现外场在线配置功能。

存储器电路包括Flash、FPGA内部同步双口两种存储器。可与C6414的(EMIF外部存储器接口,C64有2条总线EMIFA与EMIFB)连接,在使用时需通过DSP/BIOS对EMIF总线进行配置,确定访问时序。图像信息处理板上有2片Flash资源分别属于DSP和FPGA,其中属于FPGA的Flash保存的是板上控制代码,属于DSP的Flash除用以存储模块BOOT程序,还可对用户应用程序进行存储。为了采用从并方式配置FPGA,将其所属Flash连接在C6414的EMIFB异步BANK CE0,采用异步的读写信号;为支持C6414从ROM引导的机制,DSP所属Flash连接至C6414的EMIFB异步BANK CE1采用异步的读写信号。双口存储器主要用于存储帧图像数据,在图像信息处理板的FPGA上配置了双口存储器。应用中可通过FPGA设计配置同步或异步双口存储器与C6414实现数据交换,容量按图像帧大小可配置为16 kbit×16 bit,也可配置16位或32位访问方式。图像信息处理板上双口存储器连接在C6414的EMIFA同步BANK ACE0空间,可配置同步方式或异步方式。

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)