微控制器无需CPU即可生成同步正弦波与余弦波

嵌入式系统通常需要数模转换器 (DAC) 生成模拟电压与波形。DAC 有时用作嵌入式处理器的外置器件,有时集成至处理器中。无论哪种情况,CPU 都必须在适当时间将预期输出值写入 DAC。一般情况下我们采用定时器中断 CPU写入预期值来实现上述目的。如果 DAC 必须生成周期波形,CPU须从表格写入下一个值,递增数据表指针 (table pointer),并且检查表格边界,以便确定何时复位数据表指针。

将周期值写入 DAC 的过程要求 CPU 开销保持输出波形。所需要的 CPU 开销取决于数据表的长度、输出波形的频率以及 CPU 的工作频率。例如,为了每个周期采用 32 个数据点生成 1 个 1kHz 的正弦波,在 CPU 频率为 1MHz 情况下要求 CPU 每秒能够处理 32000 个中断信号。处理如此多的中断仅在中断之间留下 1000000 / 32000 = 31.25 个 CPU 指令周期。针对上下文切换与执行,如果每个中断服务只需要 15 个 CPU 周期,所需 CPU 开销就会达到近 50%。

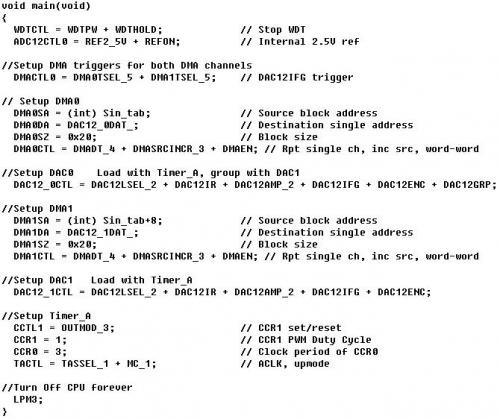

如果应用要求第二个模拟输出波形,那么 CPU 负载将会增大,甚至在所需的中断服务时间内不能更新两个 DAC。 MSP430F15x/16x 器件是解决该问题的良好方案。这些器件集成了两个 DAC 与 1 个 DMA 控制器。DMA 控制器的用途是在无需 CPU 干预情况下将数据从一个位置转移到另一个位置。在本例中,DMA 能够在规定时间内将数据从数据表转移到 2 个 DAC。

DMA 控制器具有三条独立的通道。每条通道在配置后都可以用于将数值在任何地址之间进行转移。因此,一个数据表可以同时用于正弦波与余弦波,而两条 DMA 通道只需存取数据表的不同部分,以便形成正弦与余弦输出。

此外,每条 DMA 通道都可以独立递增其源地址或目的地址。本例中,每条 DMA通道编程后递增其源地址,但目的地址不变,始终为其对应的 DAC 数据寄存器。

DMA 传输次数也可以配置。在每条 DMA 通道传输完已编程数据值数量之后,即可以从最初编程的源地址开始进行下一次传输,从而使每条 DMA 通道都构成一个带数据表的环形缓冲区并生成周期波形。

为移动数据值,每条 DMA 通道都需要一个触发器。本例中,来自每个 DAC 的中断标记用作其相应 DMA 通道的触发器。如果 2 条通道同时触发,则需要对DMA 通道进行优先排序,这样一来,会在其中一个接收数据的 DAC 中造成延迟,进而造成输出信号失真,因此应单独处理 DAC 更新。

加载到 DAC 数据寄存器中,当定时器触发 DAC 时,每个 DAC均能输出新的值。本例中设置由 Timer_A1 输出信号触发每个 DAC。由于 2 个 DAC 采用相同的触发信号,因此每个 DAC 的输出波形相互同步,以便保持相应的正弦/余弦关系。

下面列出完整代码以及 2 个输出波形的示波器画面。

-------------------------------------------------------------------------

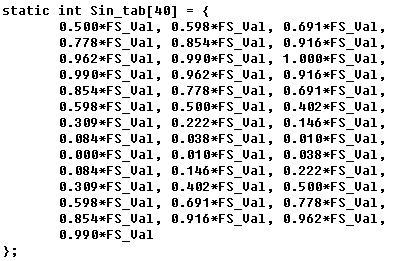

#define FS_Val 4095

最后,每次 DMA 传输都会强行占用 2 个 CPU 时钟周期。虽然 CPU 并不用于传输操作,但时钟周期的占用会造成必要的 CPU 开销且大于零。不过,对于 1kHz 的正弦波来说,假设有 32 个数据点,第 31.25个数据点之外的 2 个周期仅需要 6.4%的开销,相比之下不使用 DMA 时开销达到近 50%。另外,产生 2 个波形只需要 4个周期或 7.8% 的开销,而在不使用 DMA 时几乎不可能产生 2 个 1kHz 正弦波。

- 高带宽嵌入式应用中SoC微控制器的新型总线设计 (02-02)

- 基于红外超声光电编码器的室内移动小车定位系统(06-30)

- 基于微控制器的web服务器设计(07-04)

- 低成本ARM系列LM3S101微控制器的结构与应用(03-28)

- 嵌入式应用中的USB主设备功能(05-11)

- 爱特梅尔低功耗微控制器平台开发组合软件加速设计(02-05)