100MHz 数字存储示波表样机的研究与试制----显示数据传输电路

TMS320VC5416具有3个高速、全双工、多通道缓冲串行接口(McBSP),其方便的数据流控制可使其与大多数同步串行外围设备接口。McBSP是在标准串行接口的基础上对功能进行扩展的,除具有标准串口的功能特点外,其灵活性体现在如下几个方面:

◆双缓冲区发送,三缓冲区接收,允许连续数据流传输;

◆可与SPI、IOM-2、AC97等兼容设备直接接口;

◆可编程帧同步、数据时钟极性,支持外部移位时钟或内部频率可编程移位时钟;

◆拥有相互独立的数据发送和接收帧同步脉冲和时钟信号;

◆多通道发送和接收,最多可达128个通道,速度可为100Mbit/s.

6.2 MAX3111通用异步收发器

MAX3111通用异步收发器是MAXIM公司专门为小型微处理系统进行最优化设计的UART,它包括一个振荡器和一个可编程波特率发生器;具有一个可屏蔽的中断源;另具有一个8字节的接收FIFO(先入先出)缓冲器。它应用SPI/MICROWIRE接口技术直接与主控制器进行通信,线路简单、体积小,通信速率可达30kbit/s.另外其内部除具有UART之外,还包括两个RS-232电平转换器,这样无需再接入普通的MAX232进行电平转换,即可应用一个芯片实现微控器(具有PI/MICROWIRE接口)与PC机或其它设备之间的异步数据传输。

MAX3111通过SPI接口与主设备进行16位数据的全双工同步通信,即主设备传送16位数据给MAX3111的同时,也可接收到MAX3111发送的16位数据。主设备在MOSI线上向MAX3111发送的16位串行数据序列中包括传输格式控制字,如波特率设备、中断屏蔽、奇偶校验位等,同时还有发送的数据字。MAX3111在MISO线上向主设备发送的16位数据序列中除了接收到的数据外,还包括中断标志等状态位。所以通过16位的实时数据传输,主设备可获得MAX3111工作状态信息,同时对其具有完全控制权利。这样,两个设备的控制、状态、数据信息的实时通信就保证了数据传输的可靠性和稳定性。

6.3 TMS320VC5416与MAX3111的接口设计

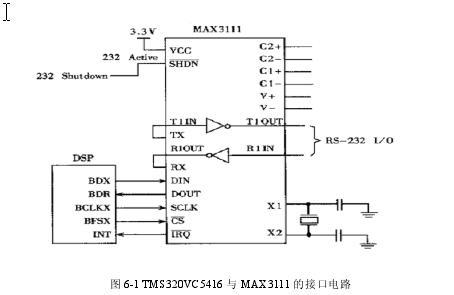

TMS320VC5416的McBSP串行接口工作于时钟停止模式时与SPI协议兼容,可直接与MAX3111进行连接,从而实现与RS-232设备进行异步数据传输。此时DSP作为SPI协议中的主设备,其接口电路如图6-1所示。

TMS320VC5416发送时钟信号(BCLKX)作为MAX3111的串行输入时钟,发送帧同步脉冲信号(BFSX)作为MAX3111的片选信号(CS)。在这种方式下对接收时钟信号(BCLKR)和接收帧同步信号(BFSR)将不进行连接,因为它们在内部与BCLKX和BFSX相连接。BDX与DIN连接作为发送数据线,BDR与DOUT连接作为接收数据线。MAX3111的TX与T1IN连接,RX与R1OUT连接,以便利用其片内的转换器实现UART到RS-232电平的转换。MAX3111的中断信号(IRQ)与DSP的外部中断相连。

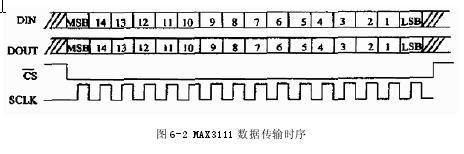

在SPI串行协议中,主设备提供时钟信号并控制数据传输过程。由MAX3111接口电路时序图6-2可知,必须设置DSP的McBSP于适当的方式才能保证与MAX3111的时序相配合。

MAX3111要求在数据传输过程中CS信号必须为低电平,在传输完毕后必须为高电平。此信号由McBSP的BFSX引脚提供,因此必须正确设置DSP的帧脉冲发生器,使之在每个数据包传输期间产生帧同步脉冲,即在数据包传输的第一位变为有效状态,然后保持此状态直到数据包传输结束。

McBSP的采样率发生器产生适当频率的时钟信号,由BCLKX引脚输出,保证主从设备间的同步数据传输。因此必须正确设置DSP的采样率发生器时钟源(CLKSM)和时钟降频因子(CLKGDV)。根据SPI传输协议,必须正确设置数据发送延迟时间(XDATDLY)。由图6-2可知MAX3111要求在SCLK变高之间的半个周期开始传输数据。

所以必须为McBSP选择合适的时钟方案,即设置McBSP的时钟停止模式。在本应用中采用McBSP的时钟停止模式2(CLKSTP=11b,CLKXP=0),这样即可保证与MAX3111的时序相配合。

结论

经过一年多的项目分析、论证、设计、制作及调试,现已完成本课题的设计任务,完成了样机的制作。本课题是"100MHz数字存储示波表"项目中数字系统部分。它是该项目的重要设计部分,通过本课题的研究,本文主要完成了以下几点:

1.数据采集系统的研究与设计。数据采集系统是数字存储示波器与模拟示波器的主要不同之处,它完成模拟信号数字化,通过实时取样和随机取样两种取样技术将模拟信号数字化。这里主要难点在于AD在高速采样率下怎样避免采样时钟的干扰和AD数据与FIFO的时序配合问题。

2.显示控制电路实现。主要设计精髓在于在没有专用控制芯片下,采用FPGA设计LCD显示时序电路,完全由硬件电路实现LCD数据显示流程以及多页面数据显示控制技术。

3.DSP与外部接口电路的设计。主要是通过MAX3111完成同步到异步的串行数据格式的转换。

同时在设计和调试过程中遇到了以下几点问题: