基于DSP的并行信号处理系统设计方案

自数字计算机问世以来,计算机的处理能力已经增长了100 k倍以上。然而,现有性能最高的计算机的计算能力仍远远不能满足人类对计算速度无止境的追求。

在科学计算、地质分析、气象预测、仿真模拟、图像处理以及实时信号处理领域,对计算机处理速度的要求尤为迫切。随着半导体技术的迅速发展,采用超大 规模集成电路设计的处理单元功能越来越强,然而单处理器性能的提高受到了诸多限制。因此,满足对运算速度的巨大需求目前只能通过并行处理技术来实现。

1 概述

本文中设计了一种并行信号处理系统,其主要特点是:

(1)具有强大的处理能力,可以完成多种信号处理模式。

(2)信号处理功能通过大量信号处理芯片(DSP)的并行计算完成。

(3)信号处理功能的改变通过软件实现。

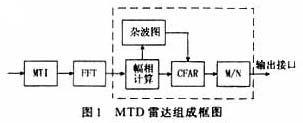

图1所示的是动目标检测雷达信号处理机的主要组成部分,虚线中的处理模块是本文要完成的工作。

2 幅相计算、CFAR检测、M/N检测

2.1 幅相计算

幅相计算指从复数据计算其幅度和相位,假使:

2.2 CFAR检测和M/N检测

雷达信号的检测总是在干扰背景上进行的,为了在强干扰中提取信号,不仅要求有一定的信噪比,而且必须有恒虚警处理设备,恒虚警处理的目的是保持信号检测时的虚警率恒定,这样才能使处理机不致因虚警太多而过载。

(1)单元平均恒虚警(CFAR)检测器

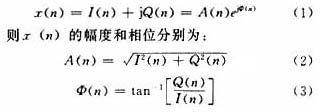

已经知道,在低分辨率的脉冲雷达中,海浪和雨雪等分布杂波可以看作很多独立照射单元回波的迭加,因而杂波包络的分布服从瑞利分布,如果检测背景中存 在此类杂波,检测门限可以通过计算杂波的均值得到,但是由于杂波在空间分布的未知性,求杂波均值只能从被检测目标邻近单元来获得,这就是比较常用的单元平 均CFAR检测器。为了减少这类检测器在杂波边缘内侧虚警显着增大问题,一般采用其改进电路-两侧单元平均选大电路,如图2所示。在被检测单元的两边,为 了防止目标本身对门限值的影响各空出了一个保护单元。

(2)二维CFAR检测器

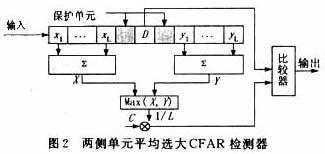

当雷达工作于FFT方式时,CFAR检测器的输入数据包括距离和频率2个变量,所以需要采用二维CFAR,如图3所示。除0# 滤波器输出送杂波图处理外,其他多卜勒滤波器输出各接一个单元平均CFAR检测器。各CFAR检测的结果合起来作为目标判断。

(3)M/N检测

M/N检测在CFAR检测后进行,其中,N为积累脉冲数,M为小于N的值。我们设定M/N检测的准则为2/3,即相同距离门的信号在3个脉冲重复周期里至少2次过门限判定有目标。

2.3 杂波图

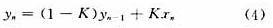

杂波图技术就是将雷达周围的二维平面分成许多方位距离单元,把方位距离单元的接收信号存入一个存储器中,每个存储单元对应一个方位距离单元,并且随着天线的扫描,每个单元存储的信号进行递推更新:

其中:K是一个小于1的因子,xn和yn分别代表输入、输出。

所以天线多圈扫描以后,杂波图中存贮的是相应方位距离单元的杂波均值。检测门限H根据式(5)计算,如果被检测信号xn大于门限H,我们就判为有目标,否则就判无目标。

H=Cyn(5)

其中:C为一个门限乘子,C的大小决定着检测概率的虚警概率。

3 系统的设计

并行处理的目的是通过采用多个处理单元同时对任务处理来减少任务的执行时间,如何能以最短的时间完成任务成为并行处理机设计者最关心的问题,对这一 问题的反映表现在处理机的2个基本性能指标:加速比和并行效率。而并行处理机的这2个基本性能决定于组成并行处理机的3个要素:处理单元、并行处理机网络 结构、并行算法程序和任务分配方法。三者之间紧密联系,互相依赖。

3.1 处理单元的选择

处理单元的性能可以说是决定处理机性能最基本的因素,高性能的处理单元可以提高系统性能、减少系统体积和功耗、降低结构复杂性和提高软件可维护性。 处理单元按应用范围大致可分为中央处理单元、专用ASIC芯片、FPGA/EPLD、数字信号处理器。在实时数字信号处理应用上,DSP仍具备明显优势。

在并行处理中,更强调DSP是否具有适于构成并行处理机的特殊功能,如高速通信口的通信能力、共享存贮器的接口功能等。TMS320C40和 ADSP21060在结构功能上有很多相似之处,相比较而言,综合性能较好地并行DSP是ADSP21060,他的运算速度、数据吞吐能力、片内存贮器容 量都远优于TMS320C40,相对于其他类型DSP.他的突出特点是:FFT速度快、片内存贮器容量大,很好地共享存贮器接口。各种兼容型号 ADSP2106X的选择余地也较大,他还与最新推出的ADSP21160代码兼容,结构与接口形式也类似。

3.2 并行处理机互联结构

并行处理机互联网络的主要功能是为各处理单元提供数据交换的通路并负责子任务传送和

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)