SoC芯片级功耗管理技术

当今的系统设计人员受益于芯片系统(SoC)设计人员在芯片级功耗管理上的巨大投入。但是对于实际能耗非常小的系统,系统设计团队必须要知道,实际是怎样进行SoC功耗管理的。他们必须对整个系统进行功耗规划。他们必须针对最终用户体验到的系统使用模式建立精确的模型。这些都不是简单的任务,把所有这些方法合在一起也还不够。系统设计人员必须要理解片内功耗管理过程以及系统其它部分之间的相互作用,或者,他们会发现,尽可能降低功耗会导致效率降低,甚至是严重的故障。

这些难题并不会随时间变化而逐渐变得简单。芯片设计人员在提高能效方面尝试了很多方法,提出了听起来非常激进的想法。在今年的设计自动化大会(DAC)的一次小组讨论中,TI专家Clive Bittlestone说:"有很多种方法,我们正在尝试全部使用它们。芯片设计人员要尽可能降低功耗而忽略了回报,可能导致加重系统设计人员的工作。而对于节能,系统设计是一个新的前沿领域。Bittlestone承认:"在晶体管级,我们已经达到了饱和。下一最关键的问题是在系统级。"

SoC设计人员所做的工作

正如Bittlestone所建议的,SoC功耗管理技术所采用的方法一直在不断增加。这包括一些很普通的方法,对管芯之外的任何东西都是透明的。但是,也有需要系统其它部分主动参与的方法,有些对外部电路还会产生重要影响。

有几种门级功耗管理方法,应用在IC设计流程中,对于系统设计人员而言是透明的。例如,对于基于单元设计的设计工具--至少一个FPGA品牌,可以在具有较大泄漏的高速单元和低泄漏电流慢速单元之间自动进行选择。综合工具可以分析逻辑,插入时钟逻辑门,关断任何寄存器的时钟,使得在其工作周期中看不到明显的数据变化。这类方法能够显著降低功耗,不需要来自系统其它部分的任何输入,对性能也不会有任何影响。

其它方法则需要来自系统管理硬件或者软件的大量帮助。一个例子是动态电压频率调整(DVFS)。在DVFS中,软件估算系统在某一模式下,模块所需要的最佳性能。然后,软件指导模块--通常是CPU或者加速器,以足够的时钟频率运行,满足系统要求,而电压则刚好满足该频率要求。同一原理更严格的方法是模块级电源选通。在这个例子中,软件确定目前还不需要模块,切断模块的电源。

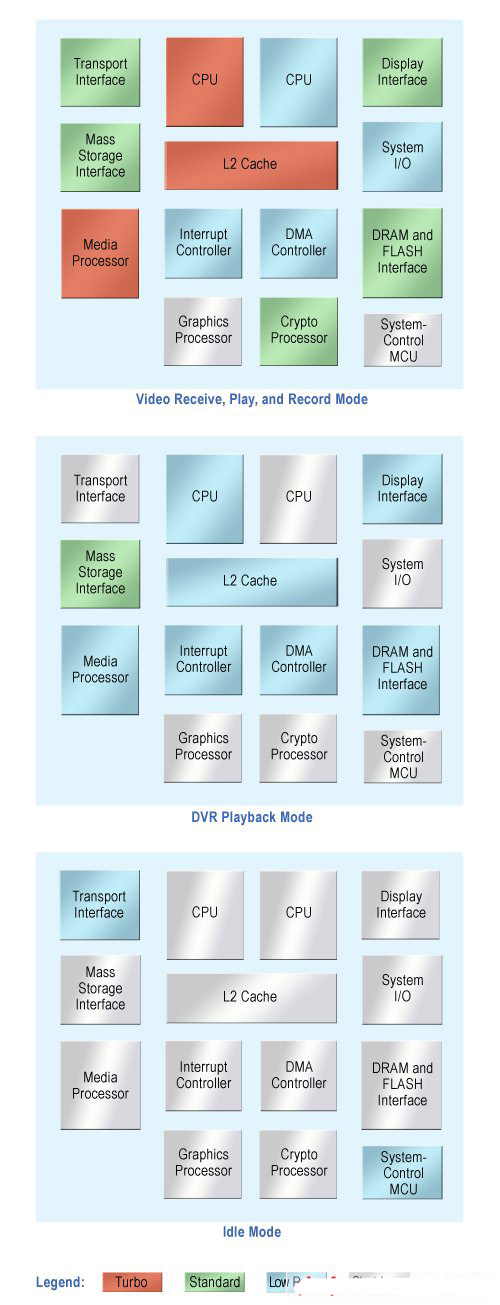

很显然,这些方法需要系统软件知道某一模式下系统的资源需求,例如 图1 所示。这些知识要求两类很难获得的信息:实际最终用户将在系统中采用的使用模式,每一模式中的系统资源和性能要求。例如,用户的智能电话要求蜂窝射频和GPS接收器同时工作吗?如果是,那么,GPS能够进入低功耗近似跟踪模式,或者,它需要进行恰当的实时纠正吗?确定模块在一定时间内需要以多快的速度运行--即使它可能会被关断,这并不是一个简单的任务。

图1.视频/播放/录像模式(顶部)、DVR回放模式(中间),以及空闲模式(底部)所需要的系统资源。

除了上面的信息,系统设计人员必须理解SoC各种功耗模式的延时和开销成本。相对而言,这可能需要很长的时间来改变CPU的时钟频率,使其能够保持状态,关断,然后重新恢复。系统中的其他器件能够承受这些延时吗?当系统空闲时,CPU内核能够关断吗,或者需要电源失效以及唤醒等监控功能吗?

对于专用标准产品和微控制器,一般在数据表中很好的记录了序列和延时信息。不一定记录状态改变时的能耗成本。即使有记录,并不是一直能够掌握SoC中的哪些模块在一定时间内工作在哪一级。

SoC规划人员提醒说:"这些芯片非常复杂。会有很多不同的功耗管理方法同时在工作。坦白的说,对于芯片而言最重要的方法是保密的--我们并没有记录它们。"

只要您使用供应商的参考设计,按照其设计人员提供的方法进行工作,那么,朋友之间最好保持一些秘密。但是,如果您从基本芯片开始设计,以创新的方式来使用芯片,那么,您可能会有些新发现。这些发现不一定是正面的。

要知道SoC哪一部分在工作,延时会变化多少,以及这对于系统行为意味着什么等等,都是问题。但是还有更棘手的问题--片内功耗管理方法会通过电源线影响系统的其他部分。

电源线上的问题

至少有三种方法,其复杂的功耗管理技术使得系统电源设计人员的工作日益复杂--排序问题、大负载性能以及瞬变响应等。稳压器等功率IC供应商采取了很多措施来处理所有这些问题。但是,缺少参考设计时,系统设计团队不得不既进行探测又进行设计。 让我们首先看一下排序问题。几乎每一种较好的功耗管理技术都要求SoC有大量的独立电压域。任何具有多个电压域的IC都要求电源线按照一定的顺序冷启动,每次一个,或者互相跟踪。实际上,某些器件即使是突然断电时,也要求电源按照一定的顺序进行关断。如果某些电压域能够工作在几种不同的电压下--正如DVFS或者其他电压可调方案,排序可能与不同域之间内部电平移位器的状态有关。一般而言,SoC设计人员采用了内部排序电路不让系统设计人员了解复杂程度,但并不总是这样。

原理上,满足排序要求并没有难度。Afshin Odabaee是Linear Technology公司µModule®电源产品的产品市场经理,他指出,SoC多年以来一直要求进行电源排序,大部分现代电压稳压器都有支持排序和跟踪的引脚。市场上还有系统控制器产品,专门用于管理过程。

即使如此,完全满足复杂的电源管理SoC的需求,就要求SoC供应商和电源组件供应商进行密切的合作。但,还是会出现错误。在某些情况下,重要的SoC约束并没有将其放到最终记录中。对于系统中有多个SoC类芯片的情况,还是需要系统设计人员为不同芯片集成电源参考设计,确定一个器件不会违反其他器件的排序要求。

第二个问题与现代SoC功耗管理技术更直接相关一些,即,负载范围。问题是,需要大量的功耗管理工作,而且要工作的很好。低电压轨的电流需求--例如,内核逻辑供电等,会变化很大,从休眠模式的几百毫安到全功率模式时内部电路处理时钟逻辑门和电源逻辑门的几十安培。电压稳压器需要在整个范围内提供足够的稳压和波纹。特别是电流需求非常低时,稳压器必须非常高效,否则,将抵消SoC所规划的低功耗。

Odabaee建议说:"您必须定义大负载工作时的稳压器。"他提醒说,待机和全速电流输出使得稳压器判决非常复杂。传统上,设计人员会选择开关稳压器来高效满足大电流负载,但是,会为低电流模式选择线性稳压器。Odabaee说,作为更可行的解决方案,业界选择了能够跨过多个域的方法。在某些Linear Technology开关稳压器µModule器件中使用的一种方法是Burst Mode®工作。稳压器在大电流输出时正常工作,低负载时则切换到突发模式,控制器仅在偶然突发时工作。这样,它提供了足够的稳压功能,同时有效的降低了自己的能耗,而且不需要复杂的多个开关频率。

- PCB布线6大原则(09-11)

- 基于高速嵌入式系统的信号完整性分析(03-02)

- HPI接口在TI SOC的应用(10-07)

- 基于MSP430的极低功耗系统设计(05-04)

- 高带宽嵌入式应用中SoC微控制器的新型总线设计 (02-02)

- SoC前段(ARM)嵌入式系统开发实作训练(上) (02-28)