基于I2C总线的键盘电路以及驱动程序的设计

一、概述

本文介绍一种采用MAX7348 的串行I2C 总线的键盘电路以及驱动程序的设计。

I2C 需要连线少,仅需一条串行时钟线和一条串行数据线。允许多主机控制,具有裁决和同步功能,可随意添加或摘除总线上的子器件等诸多优点,所以已经被广泛应用。

二、MAX7348

MAX7348 是美国MAXIM 公司生产的2 线接口、低EMI 键盘开关和发声控制器,可监控多达40 个按键,可对按键去抖并保存在FIFO 中,去抖时间用户可在9 ~ 40ms 之间任意设置,MAX7348 自带的音调发生器在控制器的作用下可自动发出按键声和报警声,在发声期间,输出还可以设置为高电平或低电平,以驱动电子发声器、继电器或指示灯。

芯片采用400Kps,5.5V 容限2 线串行接口,工作电压2.4 ~ 3.6V,4 个I2C 地址选择。与MAX7348同系列的还有MAX7347 和MAX7349 等。

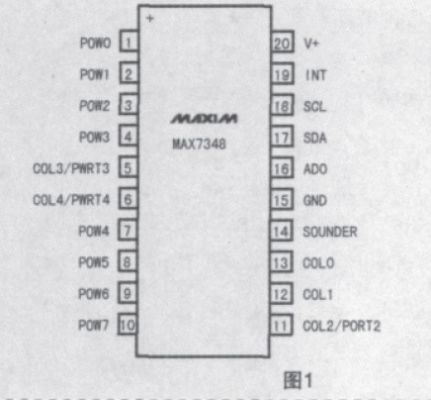

1. 引脚图

如图1 所示,SDA 、SCL 分别是兼容I2C 串行总线的数据、时钟接口,使用时通常需要接一个典型值为4.7kΩ 的上拉电阻;ROW0 ~ ROW8 为键盘矩阵行输入端口,不用时开路;COL0 ~ COL4为键盘矩阵列输出端口;SOUNDER 为发声器输出端口,该输出为推挽结构,通常与地之间接一个压电陶瓷片或其他发声设备;INT 为中断输出端口;ADO 为地址输入端口,用来设置器件的从地址,该引脚接GND、V+、SDA、SCL 可形成4 种逻辑组合构成MAX7348 的4 个可选的I2C 地址,如表1 ;GND 为接地端,V+ 接电源(2.4 ~ 3.6V)。

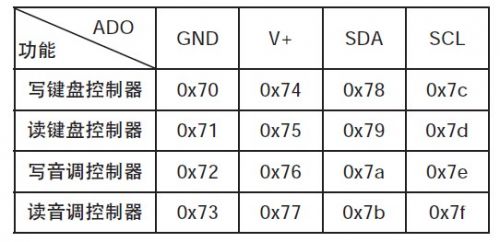

表1 2线接口地址分配表

2. 主要内部寄存器

(1) 按键FIFO 寄存器(00H) 该寄存器包含与按键FIFO 状态有关的信息,以及那些经过去抖的事件信息,该寄存器的D0 ~ D5 位表示按键中的那些键已去抖,D6 指明当前去抖按键是否是FIFO 中的最后一个;D7 位是溢出标志,它表示按键FIFO 是否溢出。读按键扫描FIFO 将清除中断信号,但是只有通过执行足够次数的读操作清空FIFO后才能再次产生中断(INT)信号。

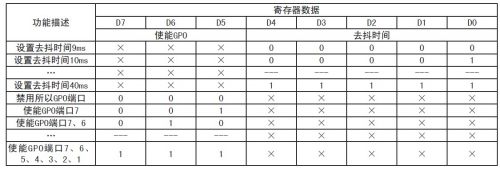

(2)去抖寄存器( 01H) 该寄存器用来设置每一个去抖周期的时间,以及使能和禁用GPO 端口,其中D0 ~ D4 位用来在9 ~ 40ms 范围内设置去抖时间,步长1ms,D5 ~ D7 用来设置使能那一个GPO 端口(表2)。

表2 去抖寄存器设置

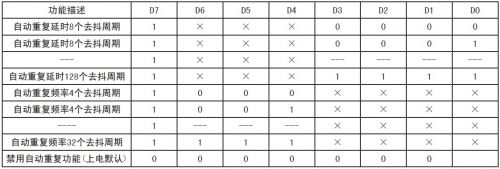

(3)自动重复寄存器( 02H)该寄存器用来设置自动重复频率及其延时。当按键按下且没有释放时,自动重复功能允许连续触发按键事件。自动重复延时规定了第一次按下按键与开始重复之间的时间(如果按键没有释放)。自动重复频率规定了自动重复开始后按键事件连续触发的速度。D0 ~ D3设定自动重复延时,范围从8 个去抖周期到128 个去抖周期。D4 ~ D6 位规定重复频率,范围是4 到32 个去抖周期,D7 位是自动重复功能使能位(如表3 所示)。

表3 自动重复寄存器

(4) 中断寄存器( 03H) 该寄存器包含与中断请求功能设置有关的信息,以及INT 输出的状态,INT 输出也可配置为GPO.中断寄存器是只读寄存器,向该寄存器写入数据无效。

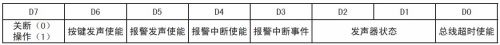

(5)配置寄存器(04H)该寄存器反映发声器的状态、控制I2C 总线超时、使能报警输入中断、使能发声器对报警输入和按键去抖时间做出响应,以及控制器件关断等。该寄存器结构如表4 所示,除D1、D2 设定发声器输出状态外,其余每一位对应一个控制状态,用户可根据需要使能(置"1")或禁止(置"0")。

表4 配置寄存器结构

(6)按键发声寄存器( 06H) 如果配置寄存器(04H)中使能按键发声,那么当一个键或一组键去抖后,发声控制器将发出声音,并由按键发声寄存器设定发声的时间和频率。

除以上几个主要寄存器外还有端口寄存器、报警声寄存器、发声器寄存器等多个寄存器,这些寄存器主要用于控制发声器和扩展GPO 端口,在此不做详细叙述,感兴趣的读者可以自行查阅有关MAX7348 的技术资料。

三、电路设计

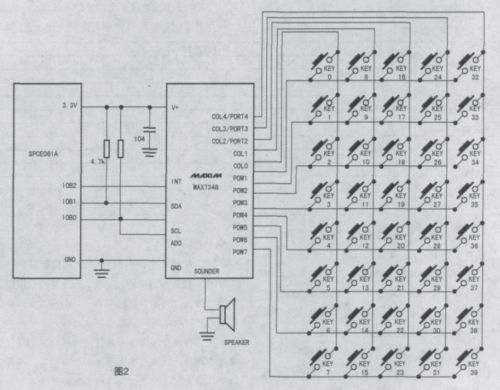

图2 是笔者设计的MAX7348 应用电路,该电路以凌阳(SPCE061A)单片机为主控制器,结合MAX7348 构成了一个具有40 个按键的键盘电路,通过程序可以设置按键发声、自动连续按键、中断输出等功能。MAX7348 的SDA、SCL、INT 分别与SPCE061A 单片机的IOB0、IOB1、IOB2(注:SPCE061A 单片机的IOB2 为外部中断1 的输入口)连接,由于I2C 总线允许挂接多个从机,所以在实际使用中,可以将多个不同从机地址的设备挂接在同一总线上,为单片机节约大量的硬件资源。

四、软件编写

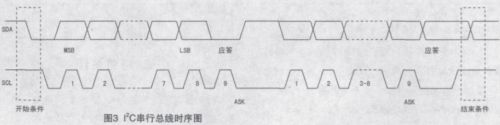

在图2 所示的键盘电路中,由于MAX7348 只具有兼容的I2C 接口,而SPCE061A 单片机本身不具备I2C 接口,要实现二者之间的数据传输,通常采用通用IO 口软件模拟I2C 的方式来实现。图3 是MAX7348 的总线时序。

由图3 所示的时序图可以看出,用软件模拟I2C 总线的传输时序,大致要经历构造开始条件、发送从机地址(含读写标志位)、等待从机响应、发送(或读取)1 个字节数据(或命令)。

笔者编写的模拟I2C 总线驱动程序,经过多次调试,程序符合I2C 总线传输时序要求,与I2C总线设备通讯可靠,但需要注意的一点是:以上代码是在SPCE061A 单片机默认时钟频率(24M)的情况下编写的,如果采用较高的系统时钟,需要在部分代码中间添加一些延时程序,否则会出现数据丢失,造成通讯错误。

- I2C总线原理及应用实例 (01-18)

- I2C总线在多机通信中的应用(01-17)

- 带RTC的I2C总线铁电存储器FM31256(01-17)

- ZLG7290在智能仪表面板接口设计中的应用(03-10)

- I2C总线多主通信研究与软件设计(07-05)

- 基于I2C的嵌入式多点触摸屏幕驱动设计(03-01)