基于共享存储器的多处理机并行快速通信

随着信息技术的发展,消费电子产品、工业仪表等电子设备对信息处理速度要求的增高,在多CPU系统当中,往往有大量的数据需要交换。通常情况下,CPU之间进行数据交换的方式有3种:串行口数据交换、I/O口数据交换和共享存储器数据交换。串行口数据交换方式是指利用CPU本身提供的串行口或在CPU芯片基础上用软硬件开发一个串行口实现双CPU数据交换,该方式实现起来相对简单,适用于两个CPU数据交换信息量不是很大,且实时性要求不高的场合。I/O口数据交换方式是指在双CPU之间增加缓冲器或锁存器实现数据交换目的,但这种方式下的数据交换信息量受到很大限制,速度也不高,适用于交换信息量很小且实时性要求不高的场合。共享存储器数据交换方式可分为两种:一种是两个CPU中的一个CPU提供直接存储器存取(DirectMemory Access,DMA)功能;另一种采用双口RAM来实现。前者两片CPU不能同时访问共享存储器,虽然数据交换信息量大,但设计复杂、编程难度大;后者可同时访问共享存储器,数据传输量大、传输速度快、接口电路简单、软件编程容易。鉴于此,本文采用双口RAM IDT7134来实现高速并行通信,多处理机选择8051系列STC89C54的8位单片机,共两片,来实现双机通信。

1 器件介绍

1.1 STC89C54单片机简介

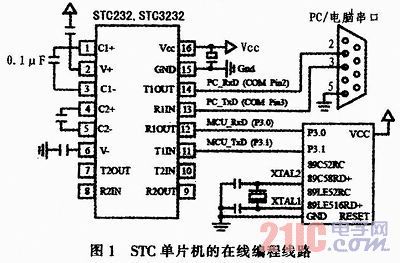

STC89C54RD+系列单片机是中国宏晶科技公司生产的8位的51单片机系列,具有低功耗,高速,抗静电,抗干扰,ISP/IAP在系统可编程/在应用可编程,无需编程器/仿真器等等特点。STC89C54的在线编程电路如图1所示。

STC89C54工作电压是5 V。工作频率可高达80 MHz。在本设计系统中选定晶振频率为22.1184 MHz。Flash程序存储器字节是16 K。RAM数据存储器字节是1 280。EEPROM字节是16 K。有2个串口UART,8个中断源,3个16位的定时器,比以前的51单片机多了4个I/O口。

STC89C54可以使用汇编语言进行设计,也可以使用Keil C语言设计,读者可以根据需要灵活使用,本文使用的是Keil C语言,调试编译成功后用STC_ISP.exe工具将生成的2进制代码或16进制代码下载到STC单片机中。

1.2 IDT7134双口RAM

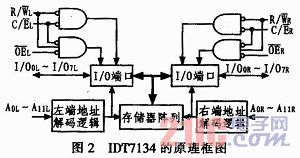

IDT7134是美国IDT公司生产的4 Kx8的4 K字节(4 Kx8位)存储容量的高速静态随机存取双口寄存器(DPSRAM)(COMS)。功耗较低:工作状态下700 mW,待机状态下1~5mW。双口RAM的每一个端口具有独立的I/O口线,地址和控制信号线,可以同时对存储器的任何地址进行操作。原理框图如图2所示。

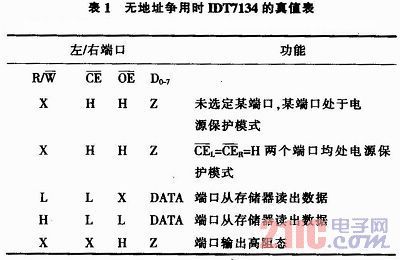

IDT7134时序与RAM的时序类似,当端口没有被选中时,即是/CE为高,无论其他端口如何配置,输出一律为高阻态;当有CPU选中某一端口时,相应端口的/CE出现下降沿,无论/OE为高还是低,只要R//W为低时,CPU对该端口进行写操作;而当/OE为低时且R//W为高时,CPU对该端口进行读操作。真值表如表1所示。

IDT7134应用在那些不能容忍等待状态的系统当中。IDT7134允许两个端口同时访问存储器,但是当两个端口同时访问存储器某个相同地址时,出现了冲突。这时用户为了保持信号完整性,必须采取一些措施。笔者采取的措施是将双口RAM分成2个区,第1个区是CPU1写,CPU2读,第2个区是CPU2写,CPU1读。两个区的数据各用两个地址空间存放标志。第一个地址空间用于告知对方此块数据是新送来的或者是已经被取走。这样两边传送数据时既不会发生同一批数据被处理两次的现象,也不会发生旧数据还未取走即被新一批数据覆盏掉的结果。第二个地址空间用于告诉对方目前该地址是使用还是没使用,以便对方做出相应的裁决,避免争用。这样做也有利于本端口使用前先查询再操作,避免争用,等待,提高了效率。

2 硬件电路设计

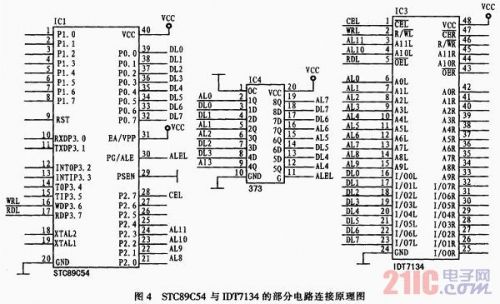

基于双口RAM的双CPU快速并行通信硬件电路设计框图如图3所示。图中左右2个CPU即CPU1(左),CPU2(右)采取在线可编程的方式从PC机得到它的程序。由于IDT7134共有4K地址,需要12根地址线查找相应的地址,用74HC373进行了P0地址的低位锁存,用P2口直接输出高位地址。CPU1把采集到的信息通过IDT7134传给CPU2做相关的处理,CPU2把自己采集、处理的信息通过IDT7134传给CPU1。

在硬件电路设计当中,尤其是在IDT7134和CPU的连接当中,特别要注意几根控制线的连接。根据STC89C54的原理和IDT7134的原理再结合经验,STC89C54的写控制P3.6接到IDT7134的写允许端口。STC89C54的读控制P3.7接到IDT7134的输出允许端口,STC89C54的P2.7接到IDT7134的片选端口。另外要注意STC89C54的ALE端要接74HC373的锁存使能G端口。STC89C54的EA端口要接高电平。图4给出了STC89C 54与IDT7134的部分连接图。

3 软件设计

定义2个IDT7134的存储区:unsignedcharxdata*xRAM1=0x0000和unsigned char xdata*xRAM2=0x0800,既是把IDT7134的4096个地址平分,分别作为CPU1存储,CPU2读取的存储专区1;后者作为CPU2存取,CPU1读取的专区2。在每一个专区,只允许专有的动作,其他的操作视作非法操作。

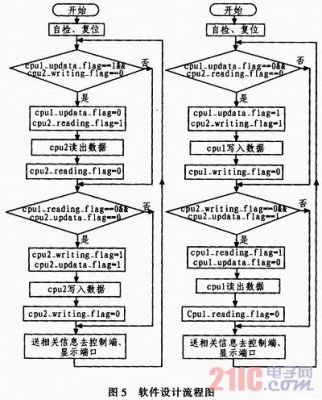

接下来第二步是设定标志位。对CPU1,CPU2的操作分别设定3个相应的标志位:CPU1有cpu1_updata_flag(为0时表示存储专区1未更新,不必读取;为1时表示存储专区1已更新,可以读取);cpu1_writing_flag(为0时表示未对该存储专区1写入操作,可以在数据有更新的情况下对该数据区进行读取;为1时表示正对该数据区进行写操作,禁止读取);cpu1_reading_flag(为0时表示未对存储专区2进行读操作,如果存储专区2的数据未更新,则CPU2可以对其进行写入操作)。同理,CPU2也有相应的3个标志:cpu2_updata_flag,cpu2_writing_flag,cpu2_ rading_flag,并具有类似的含义。

系统上电后,先自检,一切正常后,复位。复位后,所有的标志位置为0,然后进行相应的数据传输。CPU1和CPU2相应的工作流程如图5所示。

- 基于NiosII的SOPC多处理器系统设计方法(02-10)