基于高速超微型C8051F300单片机的CCD驱动电路设计

3 软件设计

为了得到时序严格的ccD驱动脉冲和外部输出同步脉冲,程序不是靠软件延时来达到合适宽度的脉冲,而是利用PCA模块本身强大的功能,用中断程序来完成各路脉冲,即开放捕捉,比较模块0的"比较匹配"中断作为同步信号,并以此为基准点完成相应脉冲的每一次变化。

3.1 CCD驱动脉冲

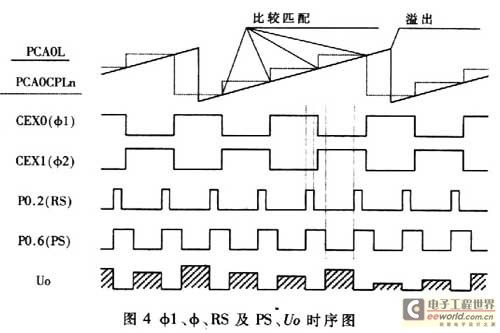

PCA的2个捕捉,比较模块工作方式设置为如图4所示的频率输出方式。其输出引脚CEX0、CEXl的初始电平设置为1、0,当PCAOL与PCAOCPLn(n=O、1)"比较匹配"时,电平翻转,由此形成反相的φ1、φ2脉冲;而HS脉冲的产生,则是在捕捉/比较模块O的"比较匹配"中断程序中,即先对RS(P0.2)置l,随后清零,这样就可产生80ns的RS脉冲(SETB bit指令周期为2个时钟周期,即80ns)。

3.2 外部输出同步脉冲及像素电压

行同步信号FS、像素同步信号IX5均设置为低电平有效,CCD时序中φl、φ2交变后直到像素电压输出有一个延迟时间tdly(典型值为150ns),但由于捕捉/比较模块0"比较匹配"时,一方面CEXO(φ1)翻转,一方面向CPU请求中断,而中断响应时间需5个时钟周期(200ns),显然大于tdly,所以进入中断后,不必考虑tdly,可直接对PS(P0.6)清零,待合适的时间后再将PS置1.这样就产生一个低电平有效的PS信号。

CCD像素输出OS、DOS经高速运放AD8031处理后,其外部输出像素电压Uo时序如图4所示。

针对单片机在CCD时序驱动应用中存在的优缺点.选用新型高速C8051F单片机,实现CCD驱动电路,克服了单片机驱动方式存在的驱动频率低、系统资源浪费、时序间隔不均匀等缺点;具有硬件结构简单、调试编程方便、可在线调整驱动频率等优点。本文所介绍的驱动电路己应用于TCDl206,超微型的封装结构使其很容易与其他芯片一起嵌入在CCD相机中,系统运行可靠。

- 32位DSP设计中的流水线数据相关问题及解决办法(05-04)

- 适用于RISC CPU的转移指令的原理及仿真(07-26)

- 一种带Cache的嵌入式CPU的设计与实现(07-30)

- DDS流水线结构的改进(07-31)

- 基于Linux和S3C2410的嵌入式图象传输系统设计(05-24)

- 嵌入式数字摄像机配置系统设计(10-15)