基于ARM和DSP的地震加速度信号处理系统

制字,设置工作模式,然后将访问地址写入地址寄存器(HPIA),再对数据锁存器(HPID)进行读写,即可读出和写入指定的存储单元。主机由两根地址线A 、A 可以寻址到HPI接口的控制寄存器、地址寄存器和数据寄存器[51;由HBIL、HCNTL1、HCNTL0区分16位数据的高、低字节。当向HBIL=0的地址写入数据时,表示是第1个字节,向HBIL=I的地址写入数据表示第2个字节。并且在数据交互之前要设置控制寄存器中的BOB位,指示高地址在前还是低地址在前。这一步在程序初始化时由ARM来完成。DSP的片选信号接主机的nCS2,地址空间属bankz组,即0)【82000000~0x82眦DSP可以通过HINT向主机发出中断信号,通知主机一帧数据处理完毕。主机收到中断信号后读取约定的DSP内部数据空间中的数据进行显示或网络传输等处理操作。

DSP的引导装载采用HPI方式,中断2信号用于激活HPI自举模式。有两种方式可以用来获取中断2引脚上的输入信号:①将主机中断HINT与INT2直接相连:②在捕捉到DSP复位向量后的30个时钟周期内触发一个有效的外部中断INT2.由于本设计HINT信号用于向主机产生中断信号,所以HPI自举加载采用方式②。注意到在自举加载的开始,HINT引脚会产生一个有效的中断信号,所以ARM在初始化时要清除这个中断。

3.3 ARM 和DM9Ooo网络控制接口

DM90OOE是Davicom公司生产的以太MAC控制器。支持10/100 Mbps传输速率。电路使用16位总线方式进行控制。即数据总线D。~D。与芯片的SD。~SD。连接,地址线也进行相对应的连接,片选线与芯片的AEN相连。DM9000E 以太网控制器的基地址为Ox300。而总线的地址线A 与芯片的命令/数据使能端CMD相连,所以对其进行操作的地址是0x300(地址端口)和0x304(数据端口),而结合ARM 的片选线得到的32位地址为0x83000300 (地址端口)和0x83000304(数据端口)。

4 系统软件设计

传统的嵌入式系统软件设计中,由于广泛采用单任务顺序机制因而编程复杂。同时系统安全性差而导致系统频繁复位以至无法达到设计目标。本设计在软件设计中引入tzCOS-II实时操作系统,使程序设计变得非常简单,将操作系统移植到LPC2214中以提高系统实时性。

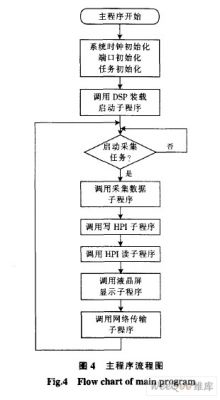

首先编写好与硬件接口的驱动程序。应用层程序以任务为编程对象。任务具有任务堆栈、优先级等参数,根据任务的执行顺序和重要程度可分配不同的优先级;在任务调度过程中可以通过OSTaskSuspend(os PRIO-SELF)、OSTaskResume(task_prio)函数进行任务之间的切换。本系统可分为DSP boot loader、 D采集、读HPI、写HPI、网络传输、液晶显示等6大任务。在主函数中创建任务,设置任务各项参数。主程序流程图如图4所示。

5 实验结果及分析

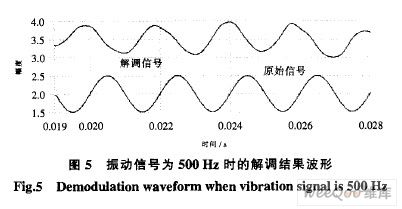

用丹麦产PM4808型振动台模拟产生地震信号,将光纤传感器输出信号输入到本系统进行解调及频谱分析网络传输测试实验,解调实验结果分别如图5所示。

从图5可以看出,系统能较准确地解调出原始信号,其误差主要来源有光纤传感耦合器的非对称、A/D量化误差、模拟电路中残留的热噪声干扰等等。

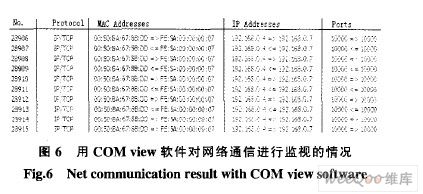

图6所示为网络数据包的传输情况。其中PC机的IP地址设置为192.168.0.4,本设计系统的IP地址设置为192.168.0.7,端*为10000.实验证明所设计的嵌入式信号处理系统可以实现基于TCP/IP的网络通信。

6 结语

本文设计的双CPU光纤传感地震加速度信号处理系统能实时地完成信号解调、频谱分析及其网络传输,系统灵敏度达4.35 V/g,支持10/100 Mbps速率的以太网传输,其提供网络控制接口对于实现传感器网络化、数据共享、远程监控等具有重要意义采用双CPU的处理方案,实现了对光纤传感地震加速度信号的高精度采集和快速处理,并具有以太网传输功能,实现了地震加速度数据的共享。

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)