高可靠平台计算机设计

引言

随着航天技术的不断发展,对控制的要求也越来越高,需要具备更高的反应速度和更强的数据处理能力。在航天领域,一旦控制发生错误,将会造成难以估计的损失。因此,如何提高控制的可靠性是长期以来的一个重要问题。本文介绍了SOC应用方式的一种实际开发方案,重点讨论了平台计算机的高可靠性的设计和实现方法。

高可靠平台计算机主要任务

本高可靠平台计算机主要完成以下主要任务:实时录取惯性测量仪表输出的转动角增量和视速度增量;接收机载导航系统给出的初始位置、速度以及姿态数据;实时接收定位卫星测量数据;实时完成制导、姿控方程的运算,按照控制律及制导律要求,对采集的信息进行变换、综合,形成控制/制导指令,控制舵机;集成1553B总线通信功能,进行总线通信与控制;4路D/A输出姿态控制指令;具有8级可屏蔽中断;通过1553B接口与地面计算机通信,进行信息交换;提供三个带光电隔离的RS422接口。

平台计算机采用FPGA + S698 IP核 的方案(简称SOC),以欧比特公司的S698 IP核做为主CPU,另外再把1553B总线控制器、VME总线控制器、3个带FIFO的UART整合在一起。体现了欧比特公司S698 IP核灵活、优越性能。并且支持多操作系统。采用SOC设计节省昂贵的流片费用、增加系统设计的灵活性、方便修改、大大缩短设计开发的周期。

高可靠平台计算机

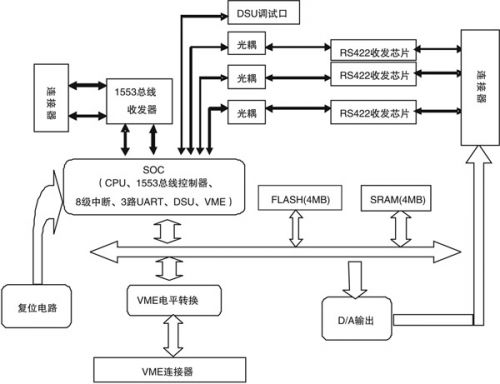

高可靠平台计算机功能框图示于图1。

图1 高可靠平台计算机功能框图

高可靠平台计算机采用FPGA+S698 IP核的SOC形式实现,FPGA采用ALTERA公司Cyclone系列EP1C20。

高性能的S698 IP核作为内核,集成了大量的外围设备,并将这些所有的模块全部集成到一个FPGA器件当中,降低了整个板级系统的成本,缩小了板级系统的体积,器件等级选用工业级以上器件,大大提高了系统的可靠性。

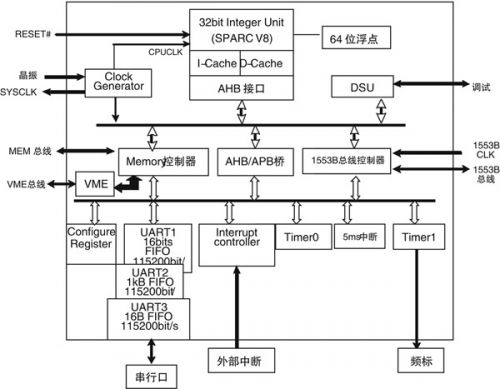

S698 IP核的功能框图示于图2。

图2 S698 IP核功能框图

S698 IP核特点如下:内部使用了5级流水线,SPARC V8指令集;硬件乘法器和除法器;支持2条DSP指令(MAC & UMAC);浮点运算:双精度(64位);具有分开的指令和数据cache结构(哈佛结构),可以根据需求灵活的配置cache的容量,大小范围是1-64kbyte;片上总线规范使用了AMBA2.0规范,支持APB,和AHB标准;外设可裁减,包括UART,定时器,中断控制器,存储器管理单元,I/O端口,看门狗等;采用AMBA AHB/APB总线结构的用户设计新模块,可以很容易加入到S698 IP核中,完成用户的定制应用;集成调试支持单元(DSU),支持硬件调试功能。

高可靠平台计算机系统板具有如下硬件资源:FPGA(集成S698、1553B、VME IP核);1553B部分;VME部分;4MB FLASH;4MB SRAM;4路+10V~-10V,12位DA输出;3路光电隔离RS422,其中2路具有16字节FIFO,1路1K字节FIFO;频标频率可配置;定时器;8级中断;FPGA提供JTAG、AS接口;1路UART;DSU(硬件调试单元)。

S698 IP核高可靠设计

为了适用于航空航天的高可靠性应用,S698 IP核采用多层次的容错策略;奇偶校验、TMR(三模冗余)寄存器、片上EDAC(检错和纠错)、流水线重启、强迫Cache不命中等。尽管现在几乎所有CPU都有一些常规的容错措施,如奇偶校验、流水线重启等,像IBM S/390 G5还采用了写阶段以前的全部流水线复制技术。IntelItanium采用的混合ECC和校验编码等技术;但远没有S698 IP核那样,采用如此全面的容错措施。

S698 IP核将时序(存储)单元的状态翻转作为数字容错的主要内容,根据时序逻辑的不同特点和性质,采用了不同的容错技术和手段。

1) Cache的容错。大的Cache对高性能CPU来说是至关重要的,而且位于处理器的关键(时间)通路上。为了减少复杂性和时间开销,错误检测的方法采用2位的奇偶校验位,l位用作奇校验,l位偶校验,因此可以检查所有的错误情况,在读Cache的同时进行校验。当校验出错误,强制Cache丢失,并从外部存储去获取数据。

2) 处理器寄存器文件的错误保护。寄存器文件是处理器内部的寄存器堆,内部的寄存器对于指令的运行速度和用户程序设计的灵活程度都是很重要的。内部寄存器的使用频率很大,其状态的正确性是也很关键。S698 IP核采用1、2奇偶校验位和(32.7)BCH校验和进行容错。

3) 触发器的错误保护。处理器的2500个触发器均采用三模冗余的方式进行容错,通过表决器来决出正确的输出。

硬件高可靠设计

3个RS422接口和1553B接口是系统对外接口,RS422采用光电隔离,工作时以光作为媒介来传递信息,无触点,寿命长,响应速度快,输入和输出在电气上是完全隔离的,采用了高等级隔离电源,给光耦单独供电,抗干扰能力强。

1553B是一种具有可确定

- 80C51原始IP核内部RAM的扩展方案(04-13)

- 一种基于PCI IP核的码流接收卡的设计(03-18)

- AMBA片上总线在基于IP复用的SoC设计中的应用(06-13)

- LEON处理器的开发应用技术文献及案例汇总(03-29)