嵌入式DSP访问片外SDRAM的低功耗设计研究

时间:03-03

来源:

点击:

4 优化后的EMIF的性能分析

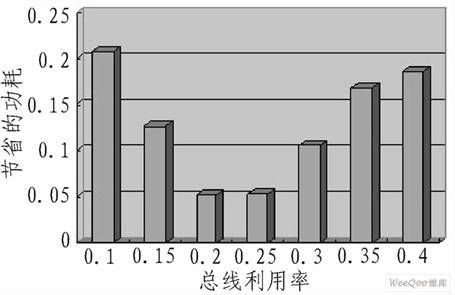

对采用的总线监测的读写归并方案进行计算,假设前后命中同一行的概率是90%,根据Micron数据手册计算,归并两个写操作功耗减少24%,对不同的总线利用率的计算结果如图3所示。

图3 基于总线监测的读写归并方案功耗计算

5 结束语

在基于DSP的嵌入式应用系统中,存储系统的功耗占据系统功耗的大部分。当外部存储器采用SDRAM时,降低SDRAM的换行访问可以节约大量的功耗。本文设计的基于总线监测的读写归并方案,不仅降低了外部存储系统的功耗,而且可以在一定程度上提高存储系统的性能。加入的I-Cache可以使程序总线更快地读指令,加入的写后缓冲区(WPB)可以使CPU不用等待缓慢的外部写操作的结束而直接继续执行指令。

- 基于NAND Flash的转译层的设计(03-11)