NAND Flash管理算法的设计及实现

时间:01-28

来源:国外电子元器件

点击:

2.4 页映射表建立时间的优化

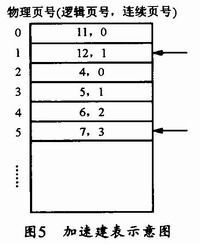

因为建立页映射表需要读取母块和子块中各物理页spare区以判定该物理页对应的逻辑页,而每个物理页的读取都要花费大约50μs的时间。因此,如果对每个物理页都读取,建立页映射表就会比较费时。为了加快建立页映射表的速度,一般只希望能读取一个物理页,而免于读取其他若干页,以便加快建表速度。因为很多时候都是连续写,而连续的几个物理页在逻辑上也是连续的,因此可以考虑在spare区加入连续逻辑页号,这样,重新建表时,就可根据连续页号知道连续几个物理页对应的逻辑页,从而加快建表的速度。对于最佳情形,有时只需要读一个页就可以建立整个逻辑块的页映射表。图5所示是一种加快建表的示意图。

2.5 分区

不同的flash,块数是不同的,其块映射表需要的RAM空间也不一样。对于当前主流flash,有的具有8192个块,如果对整个flash建表,需要的RAM空间将多达32KB,这样芯片成本就会比较高。一个可行的解决办法是对flash分区,比如1024个块为一个分区,每次只对一个分区进行建表,这样,RAM空间就可以降低到4KB。这样,随着将来flash容量的增加,块数即使再多,也能够用同样的方法处理,而不用增大RAM。

3 结束语

本文介绍了一种针对MLC flash的优异管理算法及软件实现方法,并且已在SD卡上大规模商用。该算法只需简单配置就能支持市场上的各种flash,而且也兼容各种SD设备。同时RAM空间需求小,成本低,寿命长,兼容性好,扩展性强,flash空间利用率高,具有很高的商用价值。

- NAND Flash上均匀损耗与掉电恢复在线测试(04-27)

- 用IO模拟方式读写三星系列的NAND FLASH(03-04)

- 基于ClearNAND闪存的系统设计改进方案(01-25)

- 基于NAND Flash的转译层的设计(03-11)

- 从Nand特性谈其烧录关键点(05-07)

- 存储器分类汇总,DRAM/EPROM/NAND FLASH这些行业名词你真的知道吗?(07-03)