MIPS走向更多

照片4:搞"计算"的人擅长编译优化,如这里所示,从速度、代码尺寸到编译时间,有广泛的选择空间可选

需要紧记的是,编译器优化设置(见照片4)能够产生很大影响。我试着跑过一个USB主机演示程序,采用了如表1 所示的不同编译器设置,你可以看到,不同设置下(速度/大小取向、循环展开,采取MIPS-16 的16 位代码优化选项)生成的代码大小相差能够高达2倍。

| Optimization Level | Code Size (KB) - 32-bit | Code Size (KB) - 32-bit with loop unrolling | Code Size (KB) - 16-bit |

| "0" - No optimization, debugging produces expected results | 27 | 27 | 20 |

| "1" - Reduces code size, increases speed and compile time | 20 | 24 | 16 |

| "2" - Full optimization, further increases speed and compile time | 19 | 22 | 15 |

| "s" - Level "2" optimizations that do not increase code size and others to reduce code size | 18 | 21 | 15 |

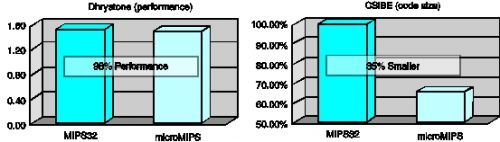

| "3" - Level "2" optimizations and function inlining | 24 | 32 | 19 表1:聪明的编译器总归不错,但是要留意可能会给调试工作带来副作用。应首选保证你的代码正确工作,然后再考虑进一步优化 保持简洁 PIC32 在精简MIPS 架构使其服务于嵌入式应用方面做得很好。比如,全部的活动功耗只有1mA/MHz 水平,从它提供的性能来看这是非常难得的。它们的批量价格也比较合理,特别考虑到那些完整的外设和存储器配备。 然而竞争也非常激烈,像Cortex - M3、瑞萨SH(现在叫RX)、爱特梅尔的AVR32 以及飞思卡尔的ColdFire 等。这些竞争对手在行业里已经有很长的时间,它们的产品也具有很广的覆盖面,在高端产品上能提供跟PIC32类似的集成度和性能,同时还有许多入门级的简单产品。 我认为MIPS 也在低端产品线上延伸,他们最近发布的"M14K"内核就是明证,在保留当前版本性能的基础上,在代码密度、中断响应和外设一致性上取得了非常大的进步。 其中最深刻的变化是一套新的"microMIPS"指令集。类似于ARM 的Thumb-2,microMIPS 采用了可变长度的操作码(16 和32 位),以同时取得两者的优点,即接近32位代码的性能和16 位代码的密度(见图2)。定长指令集是原始RISC 革命的标志性特点,这在当时是合理的(虽然我并没有觉得),但在今天,架构师们意识到用32 位存储器(即使不考虑功耗的开销)只是做个寄存器累加或短跳转是没有意义的。同上,在软件方面,编译器和IDE 都很好,但MIPS 和Microchip 也应该注意那些简单的替代产品,如ARM 的mbed、AVR 的Arduino,还有他们自己阵营的PICAXE。有些人可能还认为32 位芯片只是火箭科学家的事,但火箭能卖掉多少个?

图2:MIPS M14K进一步丢弃了"计算"架构中的包袱,如造成代码膨胀的32位定长指令,使得在保留高性能的同时,极大地减小了代码大小 想卖出更多的芯片吗?很简单,只要做到更低功耗低、更易使用、更便宜。然后接着再这样继续。 ―――――――――――― Tom cantrell 在芯片、板子和系统设计及市场推广方面有多年经验。您可以通过电子邮件tom.cantrell@ circuitcellar.com 联系他。 Tom Cantrell,发表于《Circuit Cellar》2010年8月(总第241期) |

- (独家整理)PIC系列单片机选型及应用(10-02)

- Microchip MCP3905/06电表参考设计(04-28)

- PIC单片机的应用设计技巧(07-03)

- TI在微控制器市场中奋战(05-29)

- dsPIC33FJ256MC710疑难问题及解决方法(01-22)

- 谈谈如何提高单片机的模数转换精度(01-25)