Cache��Ƕ��ʽ�������е�ʹ������

����Ƕ��ʽ�����Ӧ�õķ�չ��Ƕ��ʽCPU����Ƶ������ߣ�������������ϵͳ�洢������ƥ�����CPU���������������Ϊ�˽��������⣬��������ܵ�Ƕ��ʽ�������ڲ������˸��ٻ���Cache�����У����ǹ�˾��S3C44B0X�ڲ��ͼ�����8 KB�ռ�ͳһ��ָ�������Cache��

Cache�����ٻ���洢������λ��CPU������֮��һ��������С�����ٶȺܸߵĴ洢��������CPU�ڽ�������ʱ�������ָ������ݶ��Ǵ���������ȡ�ģ���CPU�����ٶ�Ҫ�������д�ٶȿ�ö࣬��������Ӱ������ϵͳ�����ܡ�����Cache����������Cache�д��CPU���õ�ָ������ݣ�Ȼ����Щ���ݺ�ָ����һ�����㷨�Ͳ��Դ������е��룬ʹCPU���Բ��صȴ��������ݶ����ָ��ٲ�����������������Ƕ��ʽϵͳʵʱ����Ч��Ҫ��Cache��ʹ��Ҳ������һ���Ե����⣬��Ӧ����Ӧ�ر�ע�⡣

1 Cacheһ��������ķ���

����Ŀ��Ŀ���Ϊ������������ARMоƬS3C44B0X���洢������2ƬFlash��1ƬSDRAM,�ڵ��Ե�ʱ��������ü��̣����������ʾ������RS232����ʵ��ͨ�š�

����Ŀ�Ŀ��������У�������������Գɹ��ij�������Ŀ������ȴ�����쳣��ֹ��ͨ�����洢�������ݷ��֣�����������������Ŀ����ϣ�����Ϊ�洢����д������������������ɵ����ݲ�һ�£����dz���һЩ�����ֽڡ�

����һ��ʱ��ĵ��Է��֣�ֻҪ�ڳ����н�ֹCache��ʹ�ã��洢����д������ݽ����ٷ�������������������У����ٶ����Լ�����������������Ϊ����������Cache�������������ݵIJ�һ������ɵġ�

Cache�������������ݲ�һ����ָ���ڲ���Cache��ϵͳ�У�ͬ��һ�����ݿ��ܼȴ�����Cache�У�Ҳ�����������У�����������ͬ�����һ���ԣ����ݲ���ͬ�ͽ�����һ���ԡ�������ܱ�֤���ݵ�һ���ԣ���ô��������������о�Ҫ�������⡣

2 ����Cache��һ��������

Ҫ����Cache��һ�������⣬����Ҫ�˽�Cache�Ĺ���ģʽ��Cache�Ĺ���ģʽ�����֣�дֱ��ģʽ��write��through����д��ģʽ��writeback����дֱ��ģʽ�ǣ�ÿ��CPU������д��Cache��ʱ��Cache������������������д�������Ӧλ�á����ԣ�������ʱ����Cache�����°汾���Ӷ�Ҳ�Ͳ��������潫�����ݶ�ʧ���������⡣�˷������ŵ��Ǽ�ȱ����ÿ��Cache�����и��£���Ҫ���������д�������������������Ƶ����S3C44B0X�е�Cache���Dz��õ�дֱ��ģʽ��write��through������дֱ��ģʽ�£��������ʱ��ϵͳ�������ͬʱд����ٻ���洢��Cache�������У������ͱ�֤�����ʱ���ٻ���洢����һ���ԡ�����ģʽ�£�ȴ����֤����ʱ�ĸ��ٻ���洢����һ���ԡ�

�����ٿ�һ��Cache����֯��ʽ�����������Cache֮���ӳ���ϵ��Cache��������֯��ʽ��ȫ������ʽ��ֱ��ӳ��ʽ����������ʽ�����У�ֱ��ӳ��ʽ��ԭ����ͼ1��ʾ��

ͼ1ֱ��ӳ��ʾ��ͼ

����Cache������m,�������Ϊn/m������ÿ��������m���洢�顣�����е�0~��m-1����һһ��Ӧ�ع̶�ӳ�䵽Cache��L0~Lm-1�С���������ǩֻҪ��������ַ�����ţ�������Ψһȷ��Cache����洢���Ķ�Ӧ��ϵ����CPU�����洢������ʱ���Դ洢����ַ��Ϊ��������Ѱַ��һ���ٻ����У������еı�ǩ������ǩ��洢������Ӧ��ַƥ�䣬��Cache���С��ø��ٻ����е�ǰ��Ϊ�����ʴ洢���Ψһӳ������ķ������Կ�������дֱ��ģʽ�£�����ÿ��Cache�����и��£���Ҫ���������д�������������Ƶ������Cache���еĹ����У���������������ţ��ͻ�������ݲ�һ�µ�����

3 Cacheһ��������Ľ������

��������Դ�������Ӳ�����������ֽ����

3.1 ��������ķ���

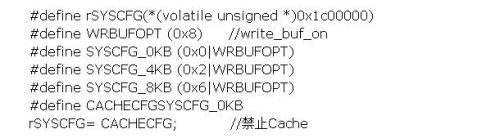

S3C44B0X��Cache�ṩ������Cacheʹ�ܺͽ�ֹ����ģʽ���ܹ�ͨ������SYSCFG�Ĵ�����CM���е�ֵΪ01��11��ʹ��Cache�����У�01Ϊʹ��4 KB Cache, 11Ϊʹ��8 KB Cache��,��ͨ�����SYSCFG�Ĵ�����[2:1]��Ϊ0����ֹCache���ܡ��ý�ֹCache�ķ������������ݲ�һ�������⣬����������£�

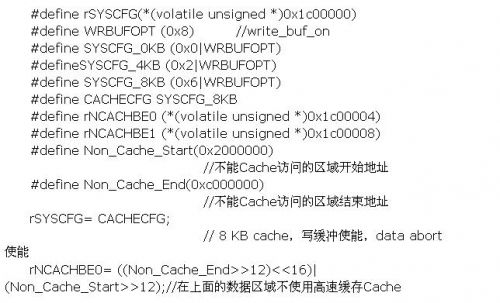

���⣬S3C44B0X���ṩ��2������Cache���ʵ�����noncacheable area����ÿ������Ҫ������Cache��������������ÿһ������Cache�����������ʼ�ͽ�����ַ���ڲ���Cache���ʵ�����Cacheû�����У�һ������ʱ��Cache���ܸ��¡�����֪Ӱ�쵽���ݲ�һ�µĵ�ַ����£�������ʹ��Cache�������£����趨����Cache��������ķ�������ֹ�������ݲ�һ��������ʱ����������������ڲ���Cache������ִ���ٶȸ��ߣ���Ϊ���������Dz������õġ����ڲ������õı�����ˢ��16 B��Cache�洢�����˷ѵġ���ϵͳ���趨����Cache���ʵ�����Ϊ0x2000000~0xc000000���Ϳ��Խ�����ݲ�һ�����⡣�������£�

һ�������� ���� CPU��Ƶ ������£�

- 32λǶ��ʽCPU��ϵͳ����Э�����������(04-19)

- ����������ͨ�ŵ�Ƕ��ʽ���ݼ�¼�豸��� (07-02)

- ����ARM��DSP�ܹ��Ķദ��������ͨ��Э�����(09-21)

- Ƕ��ʽϵͳ��һ���洢��������(01-01)

- STM32-F2ϵ��������ȫ��λ���������ϸ����(03-21)