嵌入式系统高效电源设计

,可从Maxim网站下载。

测试结果

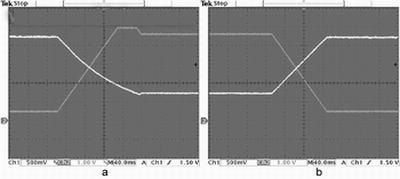

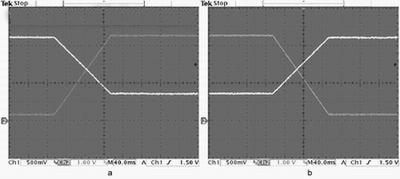

即便是满负载,该系统也可以正确地将转换器的输出电压控制在设定电压的1% 误差内。由ADC得到的反馈可以补偿负载变化、失调和输出电压漂移,以准确控制输出电压。图4a和图4b是电源电压在1mA负载时的性能,图5a表示VOUT和VDAC在VOUT 由4.5V转变到1.5V时的变化,图5b为VOUT和VDAC在VOUT 由1.5V转变到4.5V时的变化。从中可以看出VOUT的下降速率比上升速率慢很多。这是由于输出大电容放电所致(见图2的C16)。转换器可以非常快地对电容充电,但负载没有办法使电容快速放电。注意电压的变化速率非常接近,因为350mA负载可以使电容足够快地放电。这样,一个足够大的负载可以使VOUT以同样速率增加或减小。

图4 波形显示了负载电流为1mA时,降压转换器输出电压(VOUT)和DAC的输出电压(VDAC)。图a为VOUT从4.5V到1.5V变化时的VOUT和VDAC波形;图b为VOUT从1.5V到4.5V变化时的VOUT 和 VDAC波形

图5. 波形显示了负载电流为350mA时,降压转换器输出电压(VOUT)和DAC的输出电压(VDAC)。图a为VOUT从4.5V到1.5V变化时的VOUT和VDAC波形;图b为VOUT从1.5V到4.5V变化时的VOUT 和 VDAC波形

虽然电压可以准确控制,但测试结果也提醒我们系统存在的某些问题,图4a显示反馈系统会上冲或下冲。这是由软件程序循环的占用时间引起的。图4a显示VOUT达到设定值之前,VDAC增大到它的最大值。当VOUT最后达到设定值,VDAC必须减小,降低DAC输出电压需要时间,这导致VOUT下冲。理想情况下,VDAC必须和VOUT以同样速度变化,但是,在系统负载达到一定水平之前无法实现这一平衡。该系统需要100μs,用以调整大的输出电压变化,因为软件需要在ADC采样后逐位改变VDAC。为了使VOUT从5V变到1.25V,MCU必须让12位DAC的电压增加4,095次,同时对VOUT 采样4,095次,每次ADC采样都需要耗费采样时间和转换时间。