基于ADSP-TS101的高速数字电路设计与仿真

时间:06-13

来源:作者:黄军友 吕强 李焕玲

点击:

2.2 链路口仿真

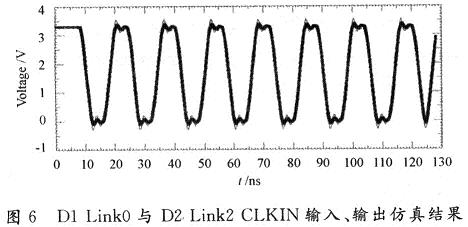

第一组:TS101 D1 Link0和TS101 D2 Link2连接LCLKIN信号,该信号印制线较长且速度要求较高(LAY 7层)。

测试条件:输入同步脉冲序列1010-1010-1010-1010,频率125 MHz,抖动10 ps,该序列为模仿CLKIN时钟信号得到的信号波形,如图6所示。

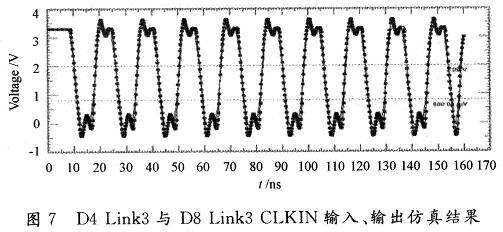

第二组抽取Lay 6层的Link走线最长的一组进行分析,以D4 Link3和D8 Link3的连接为例。思路同上,仿真波形如图7所示。

3 结 语

随着高速数字电路的发展,PCB密度、速度的提高,以及工艺方面的限制,信号完整性及电磁兼容问题会越来越突出,但只要依据一定的设计准则,通过仿真软件,可以把高速设计中的问题解决好。

ADSP-TS101 PCB 高速数字电路 信号处理系统 相关文章:

- Spartan-3 FPGA 系列中高效 PCB 布局的LVDS 信号倒相(07-27)

- 针对 Spartan-3E FT256 BGA 封装的四层和六层高速 PCB 设计(08-03)

- 蛇形走线在PCB设计中的作用(10-29)

- PCB市场概观与材料技术发展(11-03)

- PCB布线6大原则(09-11)

- ARM、FPGA和DSP的特点和区别是什么?(05-08)