嵌入式网络视频服务器的设计

嵌入式网络视频服务器是一种提供网络视频传输和共享的嵌入式设备,是为构建高可靠性的多媒体数字监控系统而设计开发的,广泛应用于分布式的安全监控、交通监控和工业监控以及家庭监控、视频会议、可视电话等众多领域。每个网络视频服务器都有自己的IP地址和网络接口,可随时随地直接接入网络,独立工作,无需专用软件、专人管理,必将成为未来数字化监控系统的发展趋势。

1 系统组成与工作原理

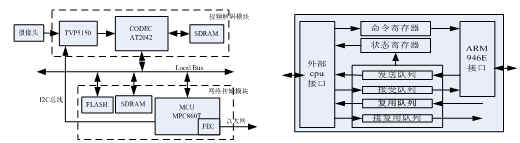

网络视频服务器系统的组成框图如图1所示。网络传输模块以MPC860T嵌入式处理器为核心处理器,完成网络传输和视频信号的实时控制功能,并采用嵌入式操作系统VxWorks作为系统的软件平台。视频编码模块主要由视频采集芯片和视频压缩芯片构成,完成信号的采集、A/D变换及压缩。CODEC选用韩国Pentamicro公司的专用音视频压缩芯片AT2042。TI公司的视频解码器TVP5150为视频采集芯片。系统初始化之后,PAL格式的模拟视频信号由TVP5150转换为ITU-R 656标准的数字视频信号,再通过数据总线进入AT2042。AT2042对数字图像信号以MPEG-4标准进行压缩编码,最后MPC860T将压缩编码后的数据流封装成IP包,通过10/100Mbps以太网接口送入Internet。

图1 系统框图 图2 AT2042与CPU的通信机制

2 视频编码模块

视频编码模块的核心是Pentamicro公司生产的AT2042,它是一个内置微控制器ARM946E的双通道音视频编解码芯片,可支持MPEG-4/2/1和JPEG标准的视频压缩编码,具有画面缩放、颜色数据格式变换、噪声抑制滤波等功能。AT2042能直接与IBM、Motorola、ARM、Xscale和Axis等多种CPU接口,无需其它附加电路。MPC860T对AT2042的控制和访问可通过AT2042的状态寄存器和命令寄存器以及四个输入输出队列:发送/接收队列,复用/解复用队列。AT2042与CPU的通信机制如图2所示。

AT2042与CPU的通信实现情况如下:CPU通过命令寄存器来控制内置微控制器ARM946E的操作状态;通过状态寄存器来检查AT2042内部各个FIFO的操作状态;通过接收队列给AT2042发送各种配置参数,以及所有内置微控制器ARM946E所需要的相关参数;通过复用队列将压缩编码后的比特流读出;通过解复用队列将需解码的比特流写入AT2042;AT2042通过发送队列向CPU发送自己的各种内部状态信息及数据[1]。

3网络传输模块

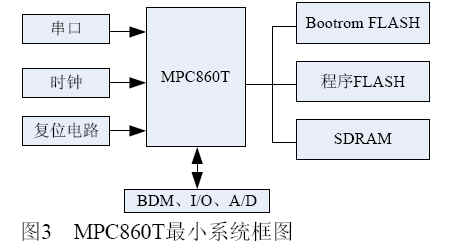

3.1 MPC860T最小系统设计

MPC860T是Motorola公司的高性能的32位PowerPC嵌入式处理器,有三个主要的功能模块:嵌入式的PowerPC内核、RISC通信处理模块(CPM)和系统接口单元(SIU)。MPC860有两个CPU:PowerPC和32位RISC。PowerPC执行高层代码,RISC处理实际通信的低层功能,2个处理机互相配合工作。这种双处理器构架,分担了主CPU的工作量,提高了处理效率,同时降低了芯片功耗,特别适合于各种通信及控制领域的嵌入式应用。MPC860T最小系统如图3所示,包括MPC860T、时钟电路、复位电路、SDRAM、FLASH、RS232口和BDM口等部分。

3.1.1 电源

电源作为一个系统的能量提供者,在整个系统设计中成为必不可少且至关重要的一个环节。MPC860T的工作电压为3.3V,需提供一个3.3V/1A的直流稳压电源给CPU及外围电路。采用外接电源适配器完成AC 220V到DC 5V的转换,DC 5V到 DC 3.3V的转换由高度集成的TI电源模块TPS75233来完成。

3.1.2 时钟电路

MPC860时钟系统为所有片上或片外设备提供不同的时钟。MPC86OT一共有两个参考时钟源,一个是其工作频率的晶振,连接EXTCLK脚,一个是32KHz的晶体,连接EXTAL和XTAL脚。设计中,两个外部时钟源都用到了。EXTCLK外接一个5MHz的晶体振荡器作为SPLL的参考时钟源,在EXTAL和XTAL之间接一个32.768KHz的晶体作为实时时钟的参考时钟源。系统启动初始化完成进入稳定的工作状态时,通过配置PLPRCR使得倍频因子MF=10,即MPC860T的正常工作频率是50MHz。

3.1.3 复位模块

MPC860T包括上电复位、外部硬复位、内部硬复位、JTAG 复位、外部软复位和内部软复位。复位电路采用MAX811T来实现。上电和人工按键均可产生复位信号,其中/RESET端口接MPC860T的/PORESET,由/RESET产生复位信号复位处理器。由SN74LVTH125芯片组成的电路提供/HRESET和/SRESET复位功能。手动按下按键连接芯片/OE控制三态门的输出使能时,低电平输出到/HRESET或/SRESET,MPC860T响应复位动作。正常状态下,输出呈现高阻状态。硬件复位字电路使用一片SN74LVC16244A来实现。

3.1.4 存储系统设计

MPC860T的存储控制器最多可以控制8个存储体或外围设备,支持GPCM (general purpose chip select machine)和UPM(User programmable machines)两种方式,可提供与SRAM,EPROM,FLASH,DRAM,SDRAM等设备的无缝连接。GPCM提供与EPROM,SRAM,FLASH以及其他的外设的无缝连接,UPM则常常用于SDRAM以及猝发式SRAM的控制与连接。Flash存储器是一种电可擦除、可重写的存储设备。Bootrom Flash采用512Kbyte的SST39VF040。Bootrom主要作用是引导及初始化CPU,以及引导单板程序。BSP(Board Support Package)就是烧写在Bootrom里的。MPC860T复位之后自动使/CS0有效,故Bootrom的片选信号为/CS0。程序Flash主要是存放网络协议、应用程序、配置监控程序。采用4Mbyte的程序Flash,片选信号为/CS1。

考虑存储容量、功耗等因素,数据存储器多选高速动态随机存储器SDRAM。Micron公司生产的MT48LC4M16A2作为SDRAM芯片,组织形式为1M X 4 bank X 16位,总容量为64Mbit,采用3.3V供电,支持的最高频率为133MHz。由于其数据总线为16位,因此系统选用两片并联构成32位。SDRAM与MPC860T的连接框图如图4所示。

- 嵌入式系统的定义与发展历史(11-15)

- 嵌入式系统亲密接触(11-22)

- 嵌入式系统设计中的USB OTG方案(02-01)

- 嵌入式线控驾驶系统开发过程中设计和测试考虑(02-02)

- 一个典型的嵌入式系统设计和实现 (02-02)

- DDR SDRAM在嵌入式系统中的应用(02-07)