一种机器人视觉系统模块的设计

时间:06-14

来源:电子产品世界

点击:

一、概述

视觉技术是近几十年来发展的一门新兴技术。机器视觉可以代替人类的视觉从事检验、目标跟踪、机器人导向等方面的工作,特别是在那些需要重复、迅速的从图象中获取精确信息的场合。尽管在目前硬件和软件技术条件下,机器视觉功能还处于初级水平,但其潜在的应用价值引起了世界各国的高度重视,发达国家如美国、日本、德国、法国等都投入了大量的人力物力进行研究,近年来已经在机器视觉的某些方面获得了突破性的进展,机器视觉在车辆安全技术、自动化技术等应用中也越来越显示出其重要价值。本文根据最新的CMOS图像采集芯片设计了一种通用的视觉系统模块,经过编制不同的图像处理、模式识别算法程序本模块可以应用到足球机器人,无人车辆等各种场合。

二、设计原理

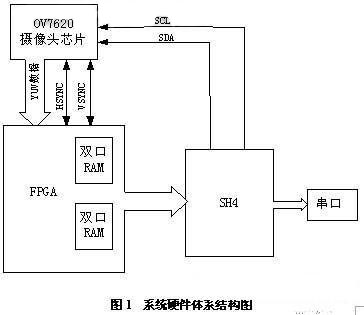

系统原理框图如图1所示。

系统包含5个主要芯片:图像采集芯片OV7620,高速微处理器SH4,大规模可编程阵列FPGA,和串口通讯控制芯片MAX232。FPGA内部编程设立两个双口RAM,产生图像传感器所需的点频,行场同步等信号,以及控制双口RAM的存储时序。SH4负责对OV7620通过I2C进行配置,读取双口RAM的图像数据,进行处理,并通过串口实现图像资料的上传或控制步进电机等其他设备。

三、图像采集模块

系统模块以CMOS图像传感器OV7620为核心,还包括一个聚光镜头和其他一些辅助元器件比如27MHZ的晶振,电阻电容等。

COMS图像传感器是近几年发展较快的新型图像传感器,由于采用了相同COMS技术,因此可以将像素阵列与外围支持电路集成在同一块芯片上,是一个完整的图像系统(Camera on Chip)。本系统采用的是Ommnvision公司推出的一块CMOS彩色图像传感器OV7620,分辨率为640x480。它能工作在逐行扫描方式下,也能工作在隔行扫描方式下。它不仅能输出彩色图像,也可用作黑白图像传感器。这块芯片支持的图像输出格式有很多种:1)YCrCb4:2:2 16 bit/8 bit格式;2)ZV端口输出格式;3)RGB原始数据16 bit/8 bit;4)CCIR601/CCIR656格式。其功能包括有对比度、亮度、饱和度、白平衡及自动曝光、同步信号位置及极性输出,帧速率和输出格式等都可以通过I2C 总线进行编程配置片内寄存器控制。

聚光镜头选用桑来斯公司生产的DSL103镜头。此镜头体积小,适合嵌入式视觉传感器的应用场合。

四、FPGA接口模块

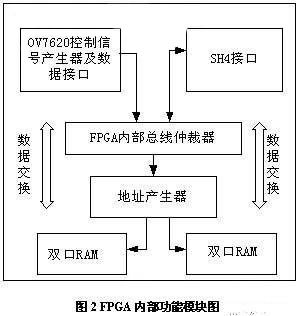

FPGA采用Xilinx公司的xc2s100,这款芯片内部集成了10000个逻辑门。接口程序采用VHDL(Very High Speed Integrated Circuit Hardware Description Language)书写。为了提高数据的传输速率,在xc2s100 内部分配了2个双口RAM缓冲区,其大小为127KB,每个双口RAM存储1行的图像数据。两组双口RAM进行奇偶行计数器进行切换。当一行存储完毕后,立即向SH4传生一个读取该行数据的中断的申请信号。FPGA内部结构如图2所示。

这里主要问题在于FPGA内部的双口RAM读写操作共用同一数据总线和地址总线,当同时进行读写操作的时候就会产生时序问题导致写入或读出的数据错误。在这两个过程中为了防止数据和地址总线冲突,在FPGA内部设计了一个中央总线仲裁器。根据公共数据传输的先后顺序,中央仲裁器先接受图像传感器的总线请求,当图像存储到RAM之中后,中央仲裁器才响应单片机系统的读信号请求。

这里给出双口RAM的构造及读写控制程序:

Entity dual_port_ram is

Generic(d_width:integer:=2;

Mem_depth:integer:=8);

Port(clk:in STD_LOGIC;

CS:in STD_LOGIC;

We: in STD_LOGIC;

Indata: in STD_LOGIC_VECTOR(7 downto 0);

Outdata:out STD_LOGIC_VECTOR(7 downto 0);

Raddr,waddr:in STD_LOGIC_VECTOR(1 downto 0));

End dual_port_ram ;

Architecture data of dual_port_ram is

Type mem_type is array(3 downto 0) of

STD_LOGIC_VECTOR(7 downto 0);

Signal mem:mem_type;

Begin

Process(clk,we,waddr)

Begin

If(rising_edge(clk))then

If(we='1')then

Mem(conv_integer(waddr))<=indata;

End if;

End process;

Process(raddr,clk)

Begin

If(rising_edge(clk))then

If(CS='0')then

Outdata<=mem(conv_integer(raddr));

End if;

End if;

End process;

End data;

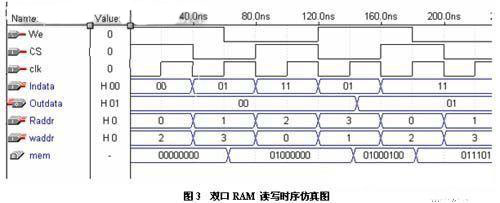

在MAX Plux II中的波形仿真图如图3所示:

五、

视觉技术是近几十年来发展的一门新兴技术。机器视觉可以代替人类的视觉从事检验、目标跟踪、机器人导向等方面的工作,特别是在那些需要重复、迅速的从图象中获取精确信息的场合。尽管在目前硬件和软件技术条件下,机器视觉功能还处于初级水平,但其潜在的应用价值引起了世界各国的高度重视,发达国家如美国、日本、德国、法国等都投入了大量的人力物力进行研究,近年来已经在机器视觉的某些方面获得了突破性的进展,机器视觉在车辆安全技术、自动化技术等应用中也越来越显示出其重要价值。本文根据最新的CMOS图像采集芯片设计了一种通用的视觉系统模块,经过编制不同的图像处理、模式识别算法程序本模块可以应用到足球机器人,无人车辆等各种场合。

二、设计原理

系统原理框图如图1所示。

|

系统包含5个主要芯片:图像采集芯片OV7620,高速微处理器SH4,大规模可编程阵列FPGA,和串口通讯控制芯片MAX232。FPGA内部编程设立两个双口RAM,产生图像传感器所需的点频,行场同步等信号,以及控制双口RAM的存储时序。SH4负责对OV7620通过I2C进行配置,读取双口RAM的图像数据,进行处理,并通过串口实现图像资料的上传或控制步进电机等其他设备。

三、图像采集模块

系统模块以CMOS图像传感器OV7620为核心,还包括一个聚光镜头和其他一些辅助元器件比如27MHZ的晶振,电阻电容等。

COMS图像传感器是近几年发展较快的新型图像传感器,由于采用了相同COMS技术,因此可以将像素阵列与外围支持电路集成在同一块芯片上,是一个完整的图像系统(Camera on Chip)。本系统采用的是Ommnvision公司推出的一块CMOS彩色图像传感器OV7620,分辨率为640x480。它能工作在逐行扫描方式下,也能工作在隔行扫描方式下。它不仅能输出彩色图像,也可用作黑白图像传感器。这块芯片支持的图像输出格式有很多种:1)YCrCb4:2:2 16 bit/8 bit格式;2)ZV端口输出格式;3)RGB原始数据16 bit/8 bit;4)CCIR601/CCIR656格式。其功能包括有对比度、亮度、饱和度、白平衡及自动曝光、同步信号位置及极性输出,帧速率和输出格式等都可以通过I2C 总线进行编程配置片内寄存器控制。

聚光镜头选用桑来斯公司生产的DSL103镜头。此镜头体积小,适合嵌入式视觉传感器的应用场合。

四、FPGA接口模块

FPGA采用Xilinx公司的xc2s100,这款芯片内部集成了10000个逻辑门。接口程序采用VHDL(Very High Speed Integrated Circuit Hardware Description Language)书写。为了提高数据的传输速率,在xc2s100 内部分配了2个双口RAM缓冲区,其大小为127KB,每个双口RAM存储1行的图像数据。两组双口RAM进行奇偶行计数器进行切换。当一行存储完毕后,立即向SH4传生一个读取该行数据的中断的申请信号。FPGA内部结构如图2所示。

|

这里主要问题在于FPGA内部的双口RAM读写操作共用同一数据总线和地址总线,当同时进行读写操作的时候就会产生时序问题导致写入或读出的数据错误。在这两个过程中为了防止数据和地址总线冲突,在FPGA内部设计了一个中央总线仲裁器。根据公共数据传输的先后顺序,中央仲裁器先接受图像传感器的总线请求,当图像存储到RAM之中后,中央仲裁器才响应单片机系统的读信号请求。

这里给出双口RAM的构造及读写控制程序:

Entity dual_port_ram is

Generic(d_width:integer:=2;

Mem_depth:integer:=8);

Port(clk:in STD_LOGIC;

CS:in STD_LOGIC;

We: in STD_LOGIC;

Indata: in STD_LOGIC_VECTOR(7 downto 0);

Outdata:out STD_LOGIC_VECTOR(7 downto 0);

Raddr,waddr:in STD_LOGIC_VECTOR(1 downto 0));

End dual_port_ram ;

Architecture data of dual_port_ram is

Type mem_type is array(3 downto 0) of

STD_LOGIC_VECTOR(7 downto 0);

Signal mem:mem_type;

Begin

Process(clk,we,waddr)

Begin

If(rising_edge(clk))then

If(we='1')then

Mem(conv_integer(waddr))<=indata;

End if;

End process;

Process(raddr,clk)

Begin

If(rising_edge(clk))then

If(CS='0')then

Outdata<=mem(conv_integer(raddr));

End if;

End if;

End process;

End data;

在MAX Plux II中的波形仿真图如图3所示:

|

五、

- 基于ARM处理器的CAN-Ethernet通信模块实现(07-10)

- 应用于智能手机的的高性能、小封装逻辑电平转换方案(06-03)

- 基于80C196KC的CAN总线智能数据采集模块设计(09-05)

- 基于TMS320F2812的最小系统设计(06-26)

- 基于ATMEGA64L和TRH031M的RFID读卡器设计 (02-15)

- ESPU安全模块实现嵌入式版权保护(02-15)