����SystemC��ϵͳ��оƬ��Ʒ����о�

ʱ�䣺05-16

��Դ��EDN

�����

4 ����SystemC�����˼����������

������SystemC�����ڳ����εIJ�ͬ������ϵͳ����ϵͳ��߲��ϵͳ��������C/C++����ϵͳ�Ĺ��ܺ��㷨����ϵͳ��Ӳ��ʵ�ֲ��ֿ�������Ϊ����RTL����SystemC ������������ϵͳ������������Ȼ������C/C++�������������ң�ϵͳ�IJ�ͬ���ֿ����ڲ�ͬ�ij�������������Щ������ϵͳ����ʱ����Эͬ���������ң���SystemC������������Ҫ������ϵͳ����������������ϵͳ�IJ���ƽ̨Testbench�����ṩ�����ź�����ϵͳ�ķ��档

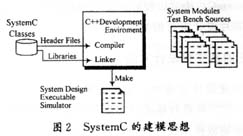

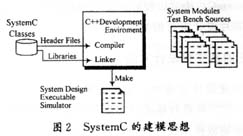

����SystemC��һ���������ͷ�ļ���һ����������˵����ӿ�Link Library����ɣ����û��Ľ�ģ���������б��������Ӧ��ͷ�ļ���Ȼ�������ͨ����C++����������ó���������LinkʱҪ����SystemC�����ӿ������ִ�е�ϵͳ�����������SystemC��ģ��˼����ͼ2��ʾ��

��������SystemC�������������ǰ��������̵ı����������ڣ�ʹ��һ�����ԾͿ�����ɴ�ϵͳ��RTL����������Ӳ����ȫ����ƣ�������Ƶ���Ӳ������Эͬ��ƺͷ��棬ǡ���ֲ��˴�ͳ��Ʒ����е���Щ���㡣

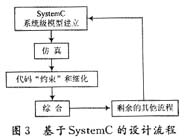

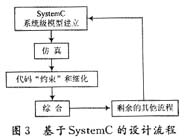

��������SystemC�����������ͼ3��ʾ��

����5 Ӧ��ʵ��

�����������һ������SystemC��Ƶ�ʵ����RS��15��9���������ϸ��˵������������̡�

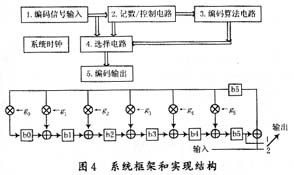

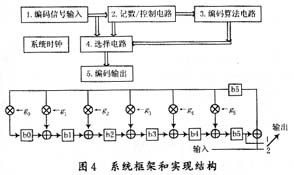

����RS(Reed-Solomon)��4�ݾ�������Ŀǰ����Ч��Ӧ����㷺�IJ�����Ʊ���֮һ����һ����к�ǿ���������Ķ���Ƶ����Է����룬RS(15,9)�����������ҪӦ�����ƶ�ͨ��ϵͳ�IJ�����ƣ����ڸñ�����С�ɡ����������ܺã������ƶ�ͨ��ϵͳ�ɿ��Ե���ߡ����ӶȵĽ�����������Ҫ�����ã�5�ݡ�����ϵͳ��ͼ4��ʾ��

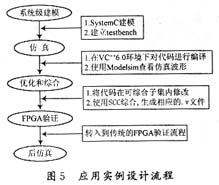

����������ƴ���SystemCΪ����ϵͳ��ģ��ʼ��ͬʱΪģ�齨��Testbench��Ȼ��ʹ��VC ++6.0��Modelsim���й��ܷ��棬������SystemC���ۺ��Ӽ��ķ�Χ�ڶԴ������Լ����ʹ��֧��SystemC���ۺϹ���SCC��SystemC Compiler������ۺϣ�SystemC���ۺ�ʵ���ϻ��ǿ��ۺ�HDL�����ļ��õ�����������SCC���������SystemC��HDL֮���һ����������˶���SystemC���ۺ������ǽ�SystemC������RTL����·ͨ��SCC�ۺϣ��ۺϵĽ����������Ӧ��Verilog�ļ��������ת������У�ģ�������ṹ�����棬��ÿһ��sc _module��ת���ɶ�����Verilogģ�飬�������module_namev�ļ��У�ÿһ�����̣�SC_METHOD����ת���ɴ���������always�飻�����Ͷ˿�Ҳ��ͬ����������Verilog�ļ������ɡ���ˣ��������̾��봫ͳ���������Ƶ�FPGA�����������ˡ�

��������ѡ��Xilinx��SPARTAN2ϵ�е�FPGA XC2S50PQ28�Ա���ƽ�����֤������ƽ̨��Ҫʹ�õ���Xilinx�ļ��ɿ�������ISE�����е���������ʹ�����ۺϹ���FPGA Compiler���ֲ��߹���ѡ�õ���ISE�е�Webpack suite��

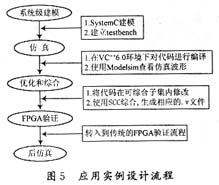

������ǰ����SystemC Compiler�ۺ����ɵ�Verilog�ļ�����ISE�У�����FC��(FPGA Compiler ��)���Դ����Լ��������ʱ��Լ��������Լ����ʱ��Ƶ�ʵȣ��������ۺϺ��Ż����õ�������������EDIF��ʽ��������벼�ֲ��߹���(webpack suite)�ӿ�,��ɲ��ֲ��߲��������ֲ�����ɺ�����һ�����ֲ��ߺ�������ļ������ӳ��ļ���SDF����һ������λb it�Ķ����������ļ�������SDF�����Ӳ���֮����ȡ����������Ԫ�����ߵ�ʱ����Ϣ��Ȼ�����Ӻ����ص�·���������������ļ���ʵ�ֶ�FPGA�����ã����ò��õ���EDAʵ���O PEN FPGA4.0����ISE���ɵ������ļ�bit�ļ���¼��FPGA XC2S50����ɡ�����ʵ��������ͼ5��ʾ��

�����Ӷ�FPGA XC2S50�����ĵ�����Դ�������Կ�����ϵͳ�ĵ�Ч��Ϊ1 124���š�

����ֵ��ע����ǣ���������ƹ����У�����ƽ̨һֱû�иı䣬��������Ʊ��������ƵĹ����У���֤�������µ���ƴ����ʼ�շ������Ҫ��

����6 ����

�����������Ŀǰҵ��Ƚ����ŵ�����ϵͳ�������SystemC����Ʒ��������������о�������Ͼ���ʵ�����������һ�������IJ���SystemC����ƽ̨��Ƶ�˼·�ͷ�����ʵ����֤���������Ŀ����ԡ�����Ŀǰ��β���SystemC������ƻ�û��һ����ȫ����ƹ淶���̣���ˣ���ν������е����˼·����������ʹ֮��Ϊͨ�ã������һ�������о����������Ż���SystemC����Ʊؽ���ΪIC�������ϵͳ����Ƶ���ѱ�֮һ��

���������

������1��Synopsys Inc.SystemC version1.0 User′s Guide.http://www.systemC.org.

������2��Synopsys Inc.SystemC version2.0 User′s Guide.http://www.systemC.org.

������3��Synopsys Inc.Functional Specification for SystemC 2.http://www.systemc.org. ��

������4��Berlekamp Elwnr.Bitserial ReedSolomon encoders��J��.IEEE Transon Information Theory��1982��IT28(6):869-873.

������5��Kwon S,Shin H.An Areaefficient VLSI Architecture of Reedsolo mon Decoder/Encoder ro Digital VCRS��J��. IEEE Trans. Consumer Electronics,199 7��43(4):1 019-1 027.

������SystemC�����ڳ����εIJ�ͬ������ϵͳ����ϵͳ��߲��ϵͳ��������C/C++����ϵͳ�Ĺ��ܺ��㷨����ϵͳ��Ӳ��ʵ�ֲ��ֿ�������Ϊ����RTL����SystemC ������������ϵͳ������������Ȼ������C/C++�������������ң�ϵͳ�IJ�ͬ���ֿ����ڲ�ͬ�ij�������������Щ������ϵͳ����ʱ����Эͬ���������ң���SystemC������������Ҫ������ϵͳ����������������ϵͳ�IJ���ƽ̨Testbench�����ṩ�����ź�����ϵͳ�ķ��档

����SystemC��һ���������ͷ�ļ���һ����������˵����ӿ�Link Library����ɣ����û��Ľ�ģ���������б��������Ӧ��ͷ�ļ���Ȼ�������ͨ����C++����������ó���������LinkʱҪ����SystemC�����ӿ������ִ�е�ϵͳ�����������SystemC��ģ��˼����ͼ2��ʾ��

��������SystemC�������������ǰ��������̵ı����������ڣ�ʹ��һ�����ԾͿ�����ɴ�ϵͳ��RTL����������Ӳ����ȫ����ƣ�������Ƶ���Ӳ������Эͬ��ƺͷ��棬ǡ���ֲ��˴�ͳ��Ʒ����е���Щ���㡣

��������SystemC�����������ͼ3��ʾ��

����5 Ӧ��ʵ��

�����������һ������SystemC��Ƶ�ʵ����RS��15��9���������ϸ��˵������������̡�

����RS(Reed-Solomon)��4�ݾ�������Ŀǰ����Ч��Ӧ����㷺�IJ�����Ʊ���֮һ����һ����к�ǿ���������Ķ���Ƶ����Է����룬RS(15,9)�����������ҪӦ�����ƶ�ͨ��ϵͳ�IJ�����ƣ����ڸñ�����С�ɡ����������ܺã������ƶ�ͨ��ϵͳ�ɿ��Ե���ߡ����ӶȵĽ�����������Ҫ�����ã�5�ݡ�����ϵͳ��ͼ4��ʾ��

����������ƴ���SystemCΪ����ϵͳ��ģ��ʼ��ͬʱΪģ�齨��Testbench��Ȼ��ʹ��VC ++6.0��Modelsim���й��ܷ��棬������SystemC���ۺ��Ӽ��ķ�Χ�ڶԴ������Լ����ʹ��֧��SystemC���ۺϹ���SCC��SystemC Compiler������ۺϣ�SystemC���ۺ�ʵ���ϻ��ǿ��ۺ�HDL�����ļ��õ�����������SCC���������SystemC��HDL֮���һ����������˶���SystemC���ۺ������ǽ�SystemC������RTL����·ͨ��SCC�ۺϣ��ۺϵĽ����������Ӧ��Verilog�ļ��������ת������У�ģ�������ṹ�����棬��ÿһ��sc _module��ת���ɶ�����Verilogģ�飬�������module_namev�ļ��У�ÿһ�����̣�SC_METHOD����ת���ɴ���������always�飻�����Ͷ˿�Ҳ��ͬ����������Verilog�ļ������ɡ���ˣ��������̾��봫ͳ���������Ƶ�FPGA�����������ˡ�

��������ѡ��Xilinx��SPARTAN2ϵ�е�FPGA XC2S50PQ28�Ա���ƽ�����֤������ƽ̨��Ҫʹ�õ���Xilinx�ļ��ɿ�������ISE�����е���������ʹ�����ۺϹ���FPGA Compiler���ֲ��߹���ѡ�õ���ISE�е�Webpack suite��

������ǰ����SystemC Compiler�ۺ����ɵ�Verilog�ļ�����ISE�У�����FC��(FPGA Compiler ��)���Դ����Լ��������ʱ��Լ��������Լ����ʱ��Ƶ�ʵȣ��������ۺϺ��Ż����õ�������������EDIF��ʽ��������벼�ֲ��߹���(webpack suite)�ӿ�,��ɲ��ֲ��߲��������ֲ�����ɺ�����һ�����ֲ��ߺ�������ļ������ӳ��ļ���SDF����һ������λb it�Ķ����������ļ�������SDF�����Ӳ���֮����ȡ����������Ԫ�����ߵ�ʱ����Ϣ��Ȼ�����Ӻ����ص�·���������������ļ���ʵ�ֶ�FPGA�����ã����ò��õ���EDAʵ���O PEN FPGA4.0����ISE���ɵ������ļ�bit�ļ���¼��FPGA XC2S50����ɡ�����ʵ��������ͼ5��ʾ��

�����Ӷ�FPGA XC2S50�����ĵ�����Դ�������Կ�����ϵͳ�ĵ�Ч��Ϊ1 124���š�

����ֵ��ע����ǣ���������ƹ����У�����ƽ̨һֱû�иı䣬��������Ʊ��������ƵĹ����У���֤�������µ���ƴ����ʼ�շ������Ҫ��

����6 ����

�����������Ŀǰҵ��Ƚ����ŵ�����ϵͳ�������SystemC����Ʒ��������������о�������Ͼ���ʵ�����������һ�������IJ���SystemC����ƽ̨��Ƶ�˼·�ͷ�����ʵ����֤���������Ŀ����ԡ�����Ŀǰ��β���SystemC������ƻ�û��һ����ȫ����ƹ淶���̣���ˣ���ν������е����˼·����������ʹ֮��Ϊͨ�ã������һ�������о����������Ż���SystemC����Ʊؽ���ΪIC�������ϵͳ����Ƶ���ѱ�֮һ��

���������

������1��Synopsys Inc.SystemC version1.0 User′s Guide.http://www.systemC.org.

������2��Synopsys Inc.SystemC version2.0 User′s Guide.http://www.systemC.org.

������3��Synopsys Inc.Functional Specification for SystemC 2.http://www.systemc.org. ��

������4��Berlekamp Elwnr.Bitserial ReedSolomon encoders��J��.IEEE Transon Information Theory��1982��IT28(6):869-873.

������5��Kwon S,Shin H.An Areaefficient VLSI Architecture of Reedsolo mon Decoder/Encoder ro Digital VCRS��J��. IEEE Trans. Consumer Electronics,199 7��43(4):1 019-1 027.

- ARMӲ���������JTAG���ź�PIO����(02-27)

- ARMӲ������ģ�EBI���� (02-27)

- ARMӲ�����һ����Դ��ʱ�� (02-27)

- ARMӲ����ƶ�����λ���ź�λ�ڼ��������(02-27)

- ����Ƕ��ʽϵͳ��������(01-17)

- AT91ϵ��ARMӲ����Ʊʼ�(09-19)