基于NiosⅡ软核的嵌入式多路视频点播系统

数据流从硬盘流出,并发出一双沿锁存信号,SRAM控制器在该信号控制下将数据锁存入内存。直到DMA请求结束,STOP信号生效,DMA传输结束。整个过程遵守ATAPI-6协议,使用Verilog HDL描述出硬盘DMA传输过程的时序。

Switch和SRAM控制器模块主要负责在DMA传输过程中在两片 SRAM间调度数据,从而实现数据的乒乓存取。Switch模块用于完成两块RAM之间的切换及数据的分区存储。它工作于两个状态:以Flag为标志位, Flag为0时做写RAMl的操作;Flag为1时做写RAM2的操作。在DMA方式下,一次DMA读取硬盘一个扇区刚好写满一片RAM,Switch模块挂起数据写入,等待中断。当另一片RAM中的数据被全部读出后中断发生,此时Switch模块交换两片内存的读写端口地址。

2.1.2 RAM分区读写

由于系统要提供多路视频的播放,因此,在进行DMA传输的过程中需实现各路视频数据的分区读写。在写内存时,采用双时钟控制机制。若要实现32路VOD系统,将一片512 k的RAM分为32个单元,每个单元长度为16 k,定义RAM的地址为:wraddress2=wraddressl+wraddress

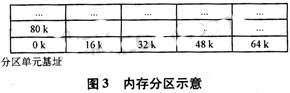

wraddressl为每个内存分区的基地址,它的取值分别是0 k,16 k,32 k,48 k,…,496 k,另外是一个偏移地址wraddress。内存分区方式如图3所示。

定义时钟C0为写内存分区时钟,C1为写内存偏移时钟,C0的频率为写C1的32倍。当偏移地址为某一值时,权值地址的取值会从0 k~496 k遍历一次,即每一内存单元读写周期,写入每个分区的一个单元。

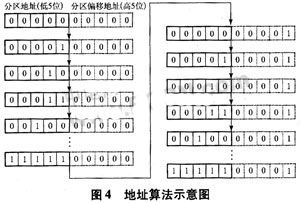

同样,对内存中的数据也要分区读出并送往相应端口。该模块使用一种内存地址的计数方法:将地址线的长度设置为10位,再将低5位的地址和高5位的地址互换,目的是从高5位开始计数,计数满了进位到低5位。高5位表示分区地址,低5位为分区的偏移地址,地址从第6位开始累加,刚好遍历32个分区,完成高5 位的依次累加后,进位到低5位的分区偏移地址,表示开始读下一轮分区的第2个内存单元。如此类推。根据计算出的地址可实现对各分区的数据依次读取。地址算法示意图如图4所示。

2.1.3 移位输出模块

该模块主要实现的功能是:在分路时钟的控制下,将从内存中读出的多路数据移位输出。该模块定义了一组长度为16位的移位寄存器。数据I/O读写的时间和速度由video_clock确定,video_clock的频率是12.5 MHz,负责控制SRAM_R控制器,移位输出模块和视频解码板的同步。模块中还设置了一个累加计数器div3,工作频率与video_clock相同。当SRAM_R控制器依次将各路视频文件读人一个寄存器后,每一个时钟下降沿到来时移出1位,直至全部移出。若加大时钟频率和缓冲内存空间,可以增加移位寄存器的数目,从而增加视频输出端口的数量,实现系统点播路数的增加。

2.2 系统软件工作流程

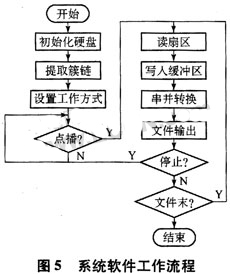

系统程序划分为主机程序和点播终端两大部分。主机程序主要实现3个功能:管理硬盘,提取簇链;播放节目,点播控制;响应请求,串口中断。管理硬盘的方式主要是通过自定义的DMA控制模块对硬盘的控制寄存器进行操作,驱动硬盘后访问FAT32文件系统下的相应扇区,追朔簇链,将簇链提取出来写入到Flash ROM中,为播放做准备。点播端程序则主要负责生成指令包。本系统软件工作流程如图5所示。

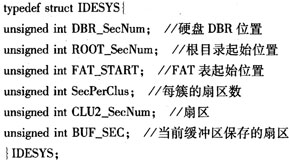

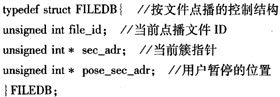

本系统要处理多路视频数据,并且视频信号数据量大,在点播过程中系统必须集中大部分处理器时间来处理各路视频信号,而视频文件的文件名和簇链结构必须通过相对低速的PIO操作来获得。为了解决簇链读取速度的瓶颈,本文设计了适合本系统应用的数据结构来优化对数据的管理,加快读取速度。定义的数据结构有:

客户端的状态和播放进度也由专门的结构体来记录和管理。定义的数据结构有:

3 结束语

SOPC =NiosⅡ软核+FPGA这个创新的概念为嵌入式设计带来的极大的便利和灵活性。利用强大的SOPC开发平台和丰富的IP资源,可大量缩短系统设计周期,而且系统的改进也变得十分方便。本文提出的通过把用户自定义的硬盘读写模块整合到SOPC平台上,与NiosⅡ无缝接合,成功实现了多路视频数据的并发点播。