分块译码的DBL 结构

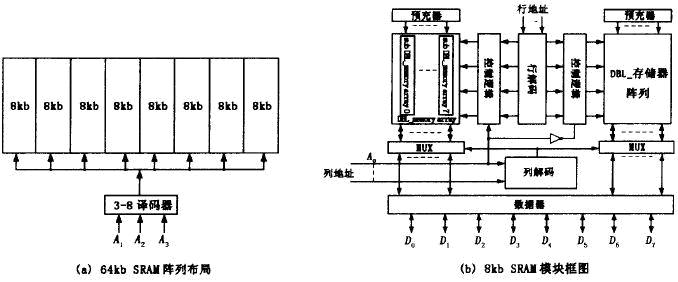

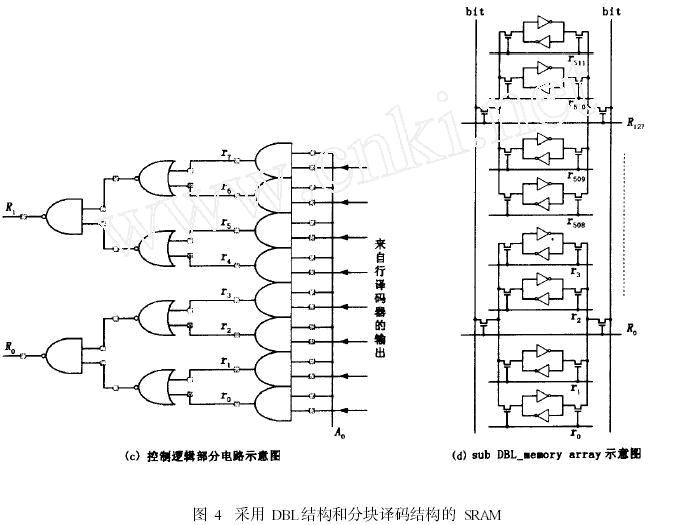

通过前面的分析可以看出,对于位线很长的存储阵列,通过采用DBL技术,选取合理的M 值,动态功耗会有所减小。 然而,以上的分析并没有考虑不同尺寸的管子以及不同的版图布局风格等因素的影响。 另外,在DBL结构中,由于还附加了其他的控制逻辑电路,其本身也有功耗,因此,实际功耗并不能完全按照公式(5)计算。为了进一步降低存储器的功耗,笔者在DBL结构的基础上,设计了存储阵列的分块译码结构。首先,为了使版图形状满足要求,将64kb SRAM划分成8个8kb的子阵列,并利用地址信号A1 , A2 , A3 译码后对8个8kb子阵列进行选择。 这不仅满足了版图的布局要求,也降低了存储器的功耗,整个布局如图4v所示。分块译码的DBL结构主要是针对每个8kb的存储子阵列设计的,如图4w所示,每个8kb的子阵列由左右两个存储阵列模块构成。 其工作原理为:利用列地址线A0 和A0 控制行译码器的输出,使得在任何读写周期,左右两个存储阵列只有一个被选中,这样整个64kb的SRAM就有1 /16子阵列处于活动状态,从而减小了由于字线充放电引起的动态功耗。

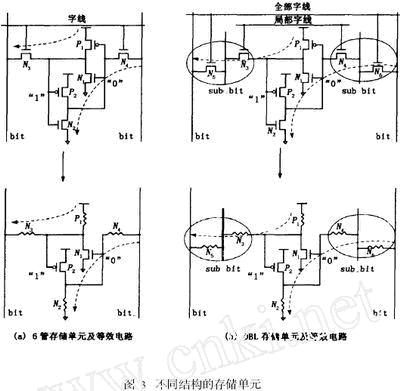

图4w中,控制逻辑的具体结构如图4x 所示,子阵列sub DBLàmemroy arrayi ( i = 0~7)的结构如图4y所示,每个子阵列有512行,即N =512,根据公式(6) ,合并后的存储单元数M =4

按照分块译码的DBL结构,采用chartered 0.35μm双层多晶三层铝布线的n阱CMOS工艺,完成了嵌入式64kb SRAM模块的设计,版图面积1。 4mm ×4. 7mm (一般结构的版图面积1.3mm ×4. 3mm)。 Starsim仿真结果表明,采用分块译码DBL结构的存储器的平均电流约为37mA,一般结构存储器的平均电流约为65mA。

结束语

以上讨论了嵌入式64kb SRAM的低功耗设计,通过采用DBL结构以及存储阵列分块译码结构,使得存储器的功耗降低了43%,而面积仅增加了18%。 仿真结果表明两者的最小访问周期都约为15 ns。 因此,根据A T2 P (A 是面积, T是访问周期, P是功耗)来衡量,这种低功耗设计方法是可行的。随着嵌入式存储器容量的加大以及深亚微米技术的发展,亚阈值漏电流所造成的静态功耗已经不可忽略,寻求有效的低功耗设计技术仍然是值得探讨的课题。