基于VxWorks的T比特路由器2.5GPOS接口板设计

1. 引言

作为因特网的枢纽,路由器正在朝速度更快、服务质量更好和更易于综合化管理的三个方向发展。现在芯片速度每18个月翻一翻,而因特网的流量是每六个月翻一翻。大家对路由器的研究也重点体现在提高路由器的处理速度上,相续提出了千兆位交换路由器(GSR,Gigabit Switch Router)和太位交换路由器(TSR,Terabit Switch Router)。

随着IP的核心地位逐渐被认同,IP over ATM、然后ATM over SDH的方式被IP直接over SDH的方式取代。传输速度也很快从OC-12 ( 622Mbps ) 跳到OC-48 ( 2.5Gbps )。POS技术已经广泛用于骨干网中,而POS接口成为高端路由器必不可少的一部分。

我所研制的T比特路由器,系统总吞吐率可达1.28Tbps,峰值交换能力为2.4Tbps,而每端口可达到10G的转发速率。为达到10G的转发速率,本路由器采用了4路2.5GPOS接口。文章在第二节描述了2.5GPOS接口的硬件体系结构的设计和性能需求分析,在第三节详细阐述了软件体系结构的设计与实现。

2. 硬件总体结构设计

本路由器硬件体系结构由线路接口子系统、转发处理子系统、光背板交换网络子系统和内部通信子系统四大部分组成。当接口收到数据包后,首先判断该包的目的地址是否为本路由器,是则上交给单板软件并由内部通信子系统交给主控处理;否则填充内部包头,注明包类型,协议类型,目的机架号,端口号,接口号等信息,由同轴电缆交给转发处理子系统,再由光背板转发到目的接口。接口把转发送过来的包和本路由器发出的包,进行和路处理后再发送出去。

2.1 性能需求分析

1)根据以往路由器的经验,通常硬件FPGA 中的高速通道工作在2.5Gbps速率下比较稳定。就A口输入数据速率10Gbps来说,4个2.5Gbps的高速通道就可以将数据传到转发处理模块。但是,线路接口模块的功能实现要求:数据包在经过线路接口输入处理模块的处理后要加上128 bit即16个byte的内部标签。考虑极限情况,A口收到的都是40 byte的超短包,那么,B口输出的数据的极限速率为:[10Gbps×(40 byte+16 byte)]/40 byte=14Gbps。所以,我们设计采用两路2.5Gbps的高速通道来传A口接收的10Gbps数据中的四分之一即2.5Gbps数据到转发处理模块。那么,B口的最大输出速率为2.5Gbps×8=20Gbps,完全满足B口传输带宽要求。

2)在均匀输入业务模型和平衡输出模型条件下,假定定长分组业务强度λ为0.95,为了控制分组的丢失概率小于10-8,可计算所需要的输出队列分组缓冲容量S约为650个分组。统计意义上IP分组的平均长度为508字节。考虑到内部分组标签附加的24字节,平均需要缓冲的IP分组字节数为532字节 总缓冲容量为650×532×8=2766400(Bits),即近似为2.8MBits的缓冲容量。

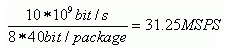

3)本子系统的接口速度要达到10Gbps,如果每个包都是40字节,那么这时极限查表速率为:

对于输入查表模块的另一个指标为表项容量。按照极限容量来算,T比特路由器有8个机架,每个机架8个端口,每个端口8个接口,每个接口的IPv4单播组播、IPv6单播组播地址总计有64个。那么极限表项容量为8*8*8*64=32768(32k)条。达到这两个设计指标是本模块设计的一个难点。最终,我们选择了一款CAM,有64K条表项,查表速率能够达到100MSPS。这样的指标完全可以达到本模块的要求。

2.2 子系统功能划分和模块设计

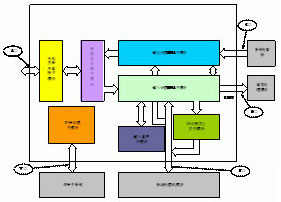

如下图所示,4 2.5G线路接口子系统可划分为光电及串并转换模块、链路层处理模块、输出FPGA处理模块、输入FPGA处理模块、协议报文上交缓存模块、输入查表模块和时钟处理模块。为描述方便,将本子系统和路由器外部的接口称为A口,和转发处理子系统的接口称为B口,和光背板子系统的接口称为G口,和单板处理机的接口称为F口,和时钟子系统的接口称为J口。

从路由器外部接收数据时,光电及串并转换模块负责从A口接收4路2.5Gbit/s串行光信号,转换成16路差分622Mhz电信号;送由链路层处理模块进行链路层处理。链路层处理模块从SDH帧提取出ppp报文,然后交给输入FPGA处理模块。输入FPGA处理模块针对输入包的类型,对输入查表模块存储的本机IP地址表查表,进行分路处理,若此报文的目的为本路由器则上交主控,否则转发到B口。输出FPGA处理模块负责接收主控下发协议包和从系统光背板转发G口数据包,合路后交给链路层处理模块。链路层处理模块把和路后的ppp报文封装在SDH帧中,由光电及串并转换模块转换成光信号发送出去。时钟处理模块为本模块提供全局时钟和将本模块从线路上提取的时钟输出到时钟板。

3. 软件总体结构

- 基于ARM7核处理器VxWorks系统BSP设计 (02-27)

- 一种嵌入式系统的内存分配方案 (03-05)

- 基于VxWorks实现自动发送彩信嵌入式设计(04-22)

- 风河增强VxWorks 653集成模块航空电子系统硬件支持(03-01)

- VxWorks下AD/DA驱动系统设计及测试(01-11)

- 如何选择ARM CPU的操作系统(05-08)