TMS320F2812慢速外设接口的时序控制

4 相关硬件设计 在实际电路设计中还需注意,由于该液晶显示模块是5 V设备,所以在连接控制线、数据线时需要加电平隔离和转换器件。可以使用74LS245芯片。 扩展了32个XCLKOUT周期,等待状态为853 ns,满足液晶模块的时序要求;但在实际应用中,由于液晶模块的显示 6 结论

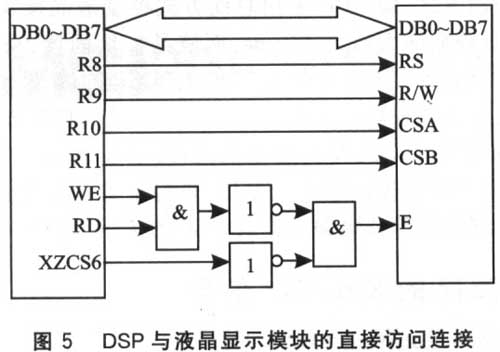

4.1 DSP与液晶模块的直接访问接口

这里,将液晶模块映射在DSP的XZCS6区上,由于制造商已经装配好了液晶显示驱动和分压电路,并提供了驱动电路接口,使得液晶显示模块和微处理器的接口十分方便。该模块共有13条信号线。RS是寄存器选择,低电平选择指令寄存器,高电平选择数据寄存器。R/w是读写控制端,低电平写显示模块,高电平读显示模块。CSA、CSB为驱动器片选信号线,可以选择相应的显示区域。E为允许输入信号线(数据读、写操作允许信号),高电平有效。DB0~DB7为数据线。功能框图如图5所示。

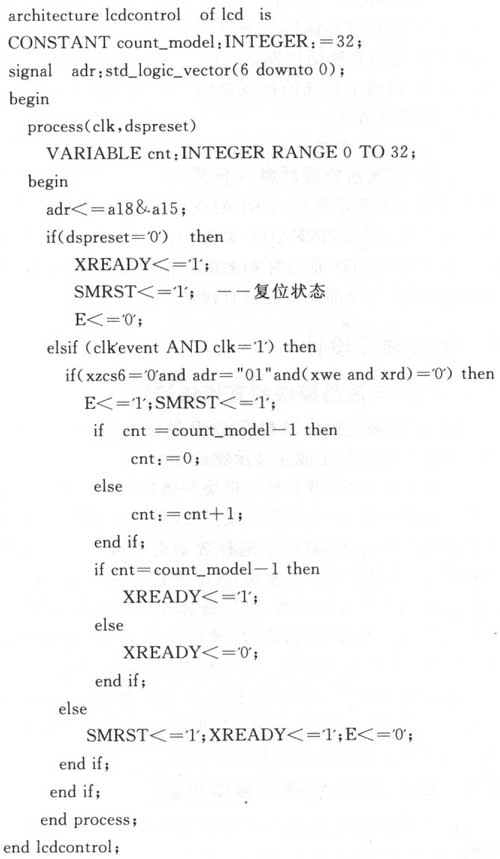

4.2基于CPLD的硬件等待电路

由于DSP芯片需要通过XREADY信号来延长读、写周期,使之与液晶显示模块的E的高电平信号相匹配,所以设计了外部硬件等待电路。该电路是通过CPLD芯片EPM7064S来实现的。EPM7064S是Ahera公司的MAX7000系列产品。它可以很容易地实现地址译码、等待时序的插入,并且是通过编写程序来实现各种逻辑的,容易修改,可移植性强,便于调试。其中,它的输入时钟为TMS320F2812的输出信号XCLKOUT。

相关VHDL语言描述如下:

速度过快,显示效果不是很好。这里,由于采用了CPLD芯片,可以修改VHDL程序,将循环次数由32次增加到146次,从而可以很方便地将等待状态延长为4 μS左右,实际效果也满足了要求。

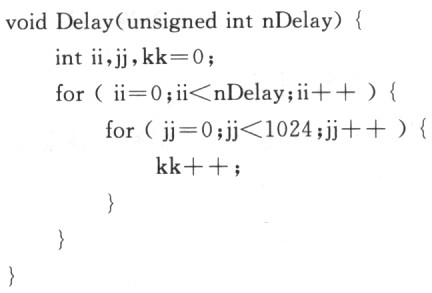

5 DSP对液晶模块连续的读写访问

当F2812对液晶显示模块进行连续的读、写操作时,两个连续的读、写周期(激活阶段)之间的时间间隔为上一个操作的跟踪阶段和这一个操作的建立阶段,最大为12个XTIMCLK周期(156 ns),不能延时。而由液晶的时序图可知,对液晶的连续两次操作的时间间隔,即使能信号E为低电平的时问,最小为700 ns。可见,两者之间时序不能匹配。于是,在连续两个命令之间加人了延时语句。虽然这种方法较之硬件实现效率要低,但完全可以满足系统的设计要求。

F2812的外部接口设计较之已有的DSP更加独立、灵活。本文给出的它与外部慢速设备时序匹配的方法,简单清楚、访问直接、控制编程容易,有助于深入了解F2812芯片的时序特点,进一步方便了该芯片的推广使用。

TMS320F2812 TI 32位 C2000 相关文章:

- 基于TMS320F2812的最小系统设计(06-26)

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 让DSP成为创新的不竭源泉(03-08)

- 在VC++中用ActiveX控件实现与单片机的串行通信(07-31)

- Whirlpool 选择赛普拉斯PSoC CapSense界面为其新型洗衣机产品实施触摸感应操控(03-24)

- MEGACHIPS采用SpringSoft CERTITUDE系统执行LSI验证(02-01)