设计灵活、高性能的嵌入式系统

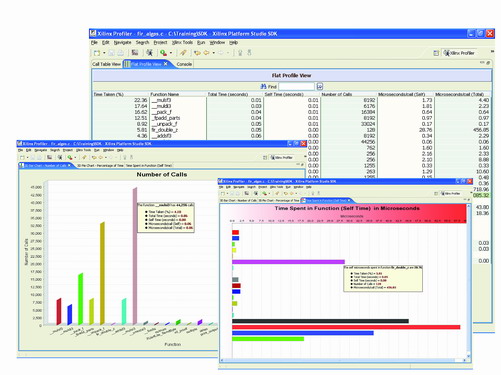

图3 - XPS嵌入式工具套件 | |

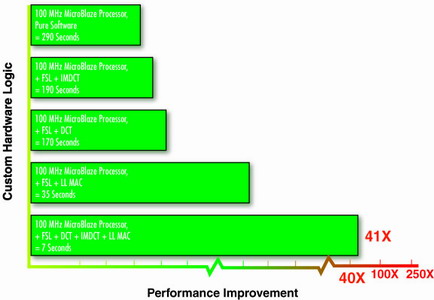

图4 - MicroBlaze MP3解码器示例 自带IP模块的软处理器核在我前面所介绍的MP3解码器示例中,我们从多个MicroBlaze处理器的示例化开始,构建了一个定制系统(图4)。由于MicroBlaze处理器是一个软核处理器,因此我们能方便地构建一个具有多个处理器的系统并能平衡性能负载,从而得到一个优化的系统。 从图4我们可以清楚地看到,顶部自带总线和外设的MicroBlaze块与底部的MicroBlaze块和它自带的外设是彼此分开的。此设计的顶部区域运行支持整个文档系统的嵌入式Linux操作系统,这样就能通过网络接入MP3比特流。我们将这些比特流的解码和播放操作留给第二个MicroBlaze处理器。在此设计中我们加入了紧密耦合的DCT/IMDCT(正向和反向改进的离散余弦变换)函数处理器减负引擎和两个高精度MAC单元。 IMDCT块负责数据的压缩和解压缩,以缩短传输线的执行时间。DCT/IMDCT是压缩应用中计算量最大的两种函数,因此将整个函数放到它自己的协处理模块中执行,极大地提高了整个系统的性能。与前面提到的在FIR滤波器中加入一个内部FPU的设计示例不同的是,这个MP3设计示例已经实现了MicroBlaze的定制,并且在FPGA中加入了外部专用硬件。

|

Xilinx FPGA Mac UART DCT IMDCT FIR FPU 相关文章:

- FPGA协同处理的优势(04-29)

- 生成有效的板支持包(04-29)

- 采用Virtex-5嵌入式三模以太网MAC进行设计(05-04)

- 使用IDELAY 实现高效8 倍过采样异步串行数据恢复(08-10)

- 基于CPLD译码的DSP二次Bootloader方法(04-08)

- 32个最热CPLD-FPGA论坛.doc(08-03)