FSL总线IP核及其在MicoBlaze系统中的应用

摘要 MicroBlaze是基于Xilinx公司新一代FPGA器件的软处理器核。其FSL 总线是FIFO单向链路,可以实现用户自定义IP核与MicroBlaze内部通用寄存器的高速直连。本文对MicroBlaze的几种主要总线接口摘要 进行比较,详细分析、介绍FSL总线的结构、特点、工作原理和配置方法。通过一个矢量汉字还原的应用实例,具体描述在FPGA片上系统设计中利用FSL高速总线整合用户自定义IP核,实现软处理器系统硬件加速的方法及步骤。

关键词 FPGA IP核 FSL总线 软核处理器 MicroBlage

引 言

随着半导体制造工艺的发展,以FPGA(现场可编程门阵列)为代表的新一代可编程逻辑器件(PLD)的逻辑资源密度不断增加,使得可编程技术很自然地就与系统芯片集成技术(SoC)的结合日益紧密,并逐步成为可配置平台技术(configurable platform)的主流。

目前,各主要PLD厂商基于FPGA的可配置平台虽然大都采用"微处理器十可编程逻辑"的架构,但在开发基于FPGA的嵌入式系统时,却采用了各自不同的方式来整合处理器系统与片上的其他逻辑资源(大多数以用户IP核形式出现)。MicroBlaze软核处理器是Xilinx公司为其FPGA器件开发的,其特有的FSL(Fast Simplex Link,快速单向链路)总线,可以实现用户IP核与软核处理器的高速连接,为设计者提供了一条解决这类问题的途径。

1 MicroBlaze软核处理器

1.1 概 述

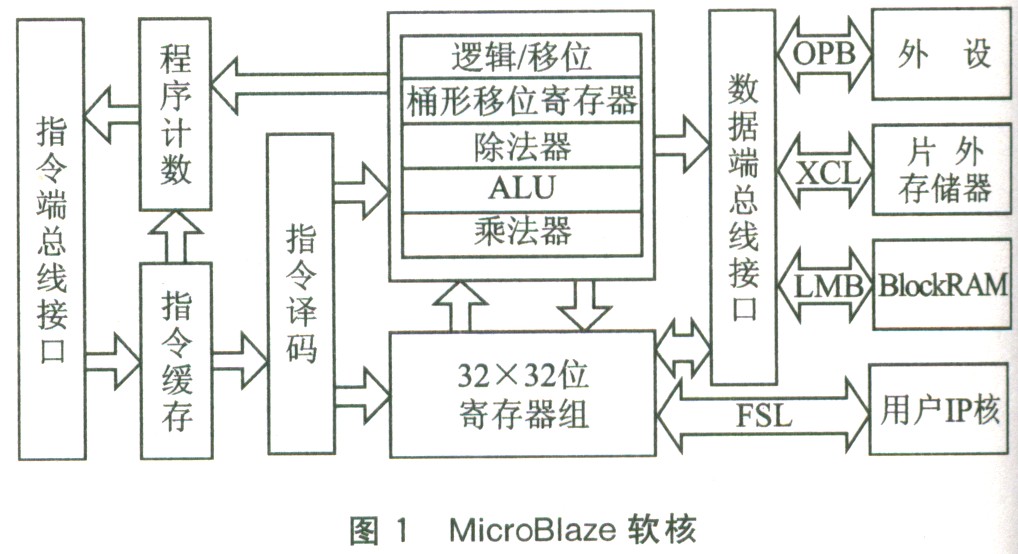

MicroBlaze是基于Xilinx公司FPGA的微处理器软IP核。它采用RISC架构和哈佛结构的32位指令和数据总线,内部有32个32位宽度的通用寄存器;在150 MHz的时钟频率下,最高可达到125 DMIPS的处理性能,其逻辑结构如图1所示(图中省略了指令侧的同类接口)。使用Xilinx公司提供的EDK(嵌入式系统开发套件),可以在参数化的图形界面下方便地完成嵌入式软处理器系统的设计。其突出的优点,一是设计灵活性;二是可以整合用户自定义IP核,使得算法可以在硬件中并行地执行而不是在软件中串行执行,从而极大地加速软件的执行速度,即所谓的硬件加速。

1.2 MicroBlaze软核总线接口

MicroBlaze软处理器核具有丰富的接口资源。目前,最新版本的MicroBlaze软核支持的接口标准有:

◆带字节允许的OPB(On-chip Peripheral Bus,片上外设总线)V2.0接口;

◆高速的LMB(Local Memory Bus,本地存储器总线)接口;

◆FSL 主从设备接口;

◆XCL(Xilinx Cache Link,Xilinx缓存链路)接口;

◆与MDM(微处理器调试模块)连接的调试接口。

OPB是对IBM Core Connect片上总线标准的部分实现,适用于将IP核作为外设连接到MicroBlaze系统中。LMB用于实现对片上的blockRAM的高速访问。FSL是MicroBlaze软核特有的一个基于FIFO的单向链路,可以实现用户自定义IP核与MicroBlaze内部通用寄存器的直接相连;而XCL则是MicroBlaze软核新增加的,用于实现对片外存储器的高速访问。MicroBlaze软核还有专门的调试接口,通过参数设置,开发人员可以只使用特定应用所需要的处理器特性。

1.3 MicroBIaze系统的硬件加速

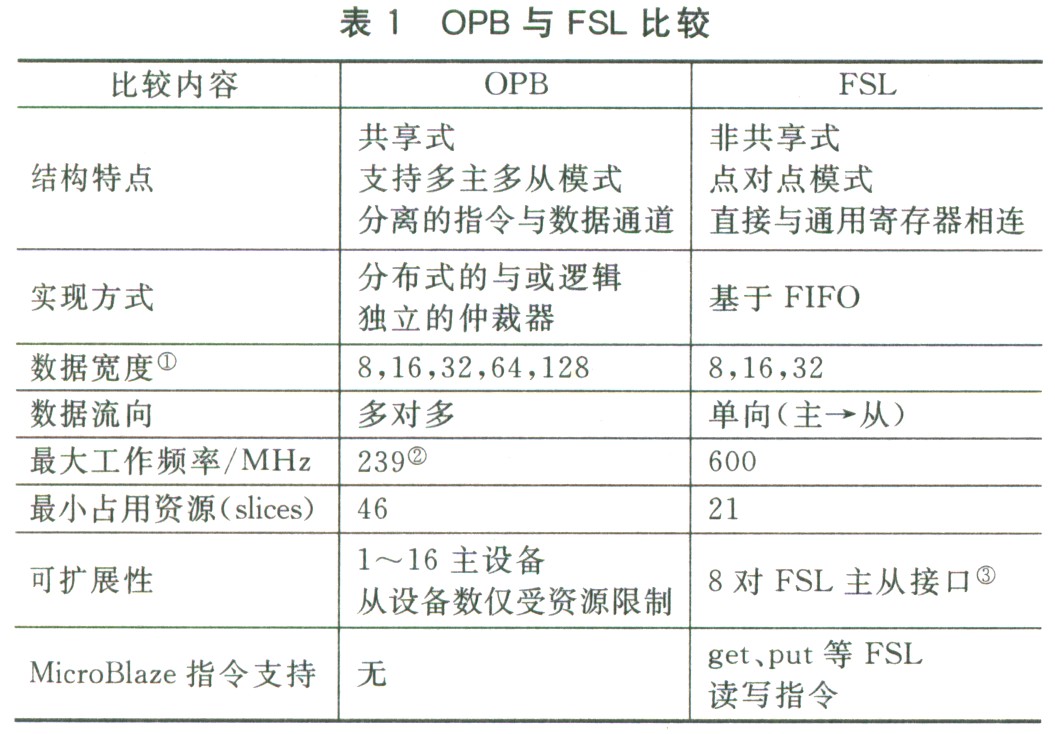

将用户IP核整合到基于MicroBlaze的嵌入式软核处理器系统中,通常有两种方法:一种方法是将IP核连接到OPB总线;第二种方法就是将用户IP连接到MicroBlaze专用的FSL总线上。OPB与FSL比较如表1所列。

注:①数据分别来自opb_v20和FSL_v20数据手册;

②该数据是在总线配置为1主2从情况下得到的;

③该数据对MicroBlaze软核而言。

从表1可见,尽管OPB和FSL都是MicroBlaze软核与FPGA其他片上逻辑资源连接的主要途径,但其特点决定了分工是不同的:OPB总线适用于将低速和低性能要求的设备连接到MicroBlaze系统中;而FSL总线则适用于将时间要求高的用户自定义IP核整合到基于MicroBlaze的软核系统中,以实现硬件加速。

2 FSL总线

2.1 FSL总线接口

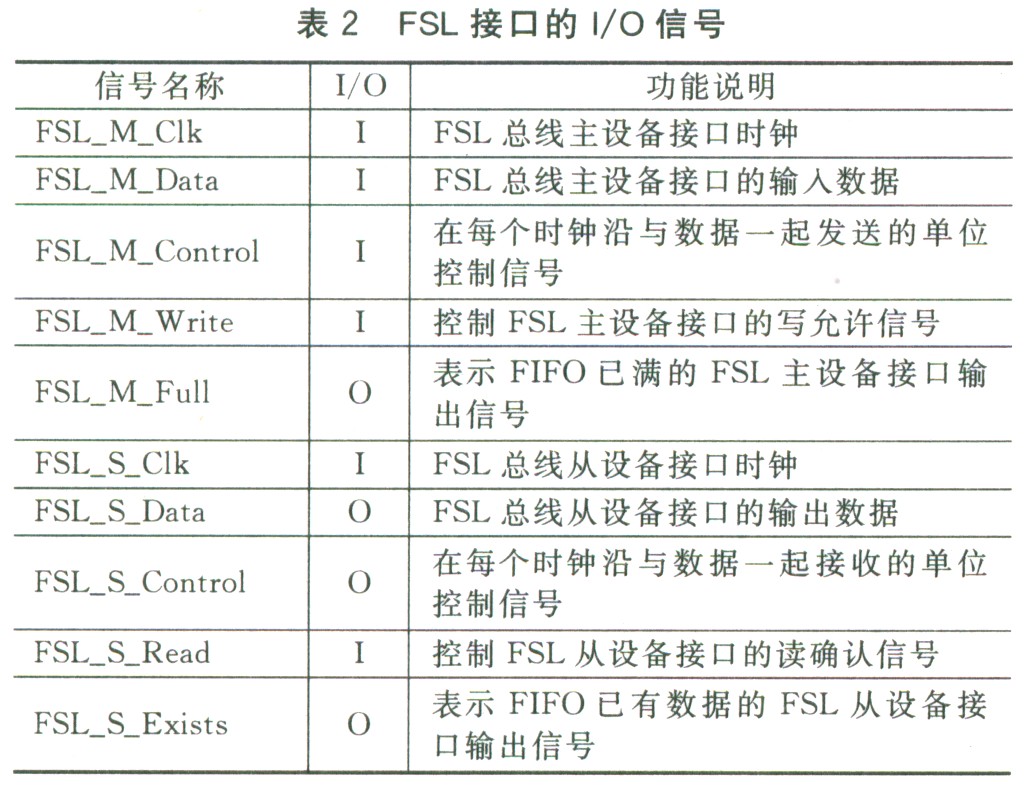

FSL总线是一个基于FIFO的单向点对点通信总线,主要用于FPGA的两个模块问进行快速的通信。FSL总线IP核结构如图2所示,FSL接口的I/O信号如表2所列。

该接口的主要特点:

◆单向的点对点通信;

◆非共享的无仲裁通信机制;

◆支持控制位与数据分离的通信;

◆基于FIFO的通信模式;

◆可配置的数据宽度;

◆高速的通信性能(独立运行达到600 MHz)。

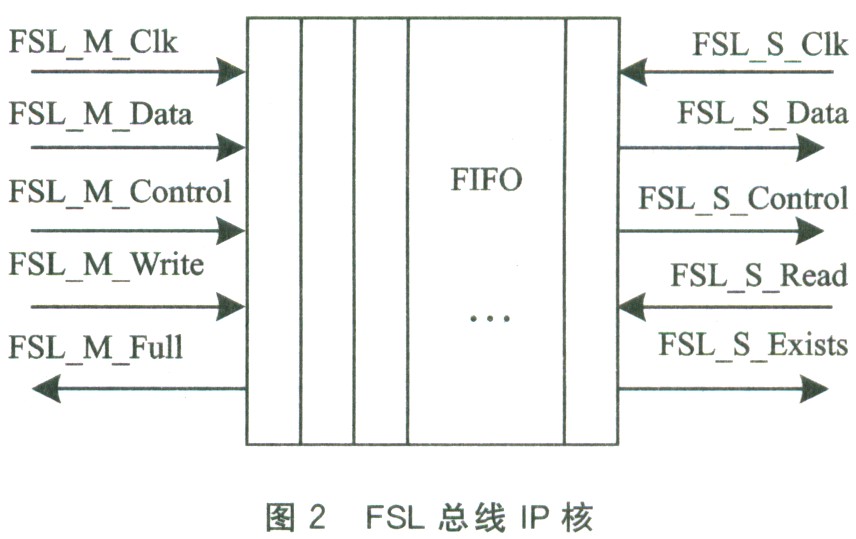

2.2 FSL总线的写操作时序

对FSL总线的写操作是由FSL_M_Write信号控制的。图3是FSL总线的写操作时序。FSL主设备在第一个时钟上升沿检查到FSL_M_Full信号未置高,就允许主设备将FSL_M_Write置高,并将FSL_M_Data和FSL_M_Control推上总线,在下一个时钟周期这些数据就被总线读取并送入FIFO了。图中的Write2和Write3是一组"背靠背"的连续写操作。在Write3时,FIFO满使得FSL_M_Full信号被置高,迫使主设备取消自己的FSL_M_Write信号,直到一次读操作将FSL_M_Full置低后,才可以发起另一次写操作。因此,图中暗示着在Write4处也发生了一次从设备的读操作,否则FSL_M_Full将再次置高。