ST-BUS总线接口模块的Verilog HDL设计

信号均来自外部,因此该模块处于被动模式;相反,如果时钟和同步信号由模块产生,则模块处于主动模式。

被动模式下ST-BUS接收模块的基本工作原理为:上电后,在时钟稳定的情况下,模块首先检测同步信号;在非同步状态下,除同步检测以外的其它部件均不能工作;检测到同步后(即在同步状态下),模块启动时隙定位和数据位定位的计数器工作,此时,模块根据参数设置进行数据接收。另外,图2(a)中的时隙定位和数据位定位在本设计中采用2个计数器实现,也可以合并为单计数器实现。ST-BUS总线接收操作的关键之处在于前一帧的最后一时隙(即31时隙)与当前帧的第一时隙(即0时隙)之间的切换操作,因为需要同时检测同步信号,而一旦同步信号没有检测到,则模块会进入失步状态。接收模块的Verilog HDL实现(信号和常数声明从略,且代码已简化,下同)可以划分为以下三部分。

(1)同步检测

if(!f0) begin file://同步信号低电平有效

f0_flag<=1; file://置同步标志

bitcounter<=bitsofbyte-1;//时隙内的数据位数减法计数器复位

bytecounter<=0; end

file://时隙数加法计数器复位

(2)定位计数

if(f0_flag) file://判断同步状态

begin case(bitcounter) file://根据数据位计数值进行时隙切换

0:begin

bitcounter<=bitsofbyte-1;

file://数据位计数器复位

bytecounter<=bytecounter+1;

file://时隙通道计数器递增

end

default:bitcounter<=bitcounter-1; file://时隙内位计数器递减

endcase end

(3)接收数据(含标志及使能信号产生)

if(bytecounter==byte_pos1) begin file://检查第1通道

din2<=8'bZ;

file://释放通道2暂存单元

receive2_flag<=0;

file://清除通道2接收标志

din1<=din1<<1;

file://移位准备接收下一位数据

din1[0]<=dr; file://读入数据位

if(bitcounter==0) begin receive1_flag<=1;end//接收完整通道数据置标志

end

else if(bytecounter==byte_pos2)

file://多通道接收(同上)

……

else begin

file://当前通道不接收数据,则释放暂存单元并清除接收标志

din1<=8'bZ;din2<=8'bZ;receive1 _flag<=0;receive2_flag<=0;end

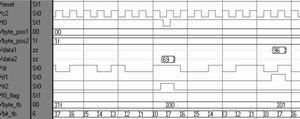

根据ST-BUS总线收发规则及接收模块基本工作原理,为了31时隙与0时隙的可靠切换,设计中采用状态转换与数据接收分开的方法,也即以上模块可由2个always语句实现,一个采用C2上升沿实现状态转换,一个采用C2下降沿实现数据接收。在Altera公司提供的Quartus II 5.0SP1集成开发环境下,利用MAX7000S系列最低性能的CPLD器件作综合后的时序仿真结果如图3(a)所示。图中第一通道为0时隙,第二通道为31时隙。

a)ST-BUS接收模块仿真

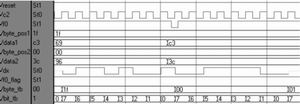

b)ST-BUS发送模块仿真

图3 ST-BUS收发模块综合后的时序仿真结果(C2时钟为10MHz)

ST-BUS发送模块

ST-BUS发送模块主要将控制模块送来的数据按照所设置的时隙进行发送,也就是将一般数据信号转换为ST-BUS总线信号,其原理结构框图如图2(b)所示。

发送模块可工作于两种模式,即主动模式和被动模式。图中细的虚线部分(除去相应的实线部分)表示工作于主动模式的连接,此时,时钟和同步信号均由模块内部产生;若除去细的虚线部分,则模块工作于被动模式。在本文涉及的E1接口板设计中,系统采用了自动模式选择的工作方式。图中同步的作用,在主动模式时为同步发生,在被动模式时为同步检测。

被动模式下ST-BUS发送模块的基本工作原理与接收模块类似,所不同之处在于数据传输方向相反。与接收模块一样,图2(b)中的时隙定位和数据位定位也可以合并采用单计数器实现。ST-BUS总线发送操作的关键之处也在于前一帧31时隙与当前帧0时隙之间的切换,因为需要同时检测同步信号,并且状态转换和总线数据加载都在C2上升沿完成。发送模块的Verilog HDL实现可划分为两部分,与接收模块划分不同,这里已把发送数据的操作嵌入到了同步检测和定位计数当中,当然也可严格按功能块划分。

(1)同步检测及数据发送

if(!f0) begin file://同步信号低电平有效

f0_flag<=1;//同步状态标志

bitcounter<=bitsofbyte-1;//位计数器复位

bytecounter<=0; file://时隙计数器复位

if(byte_pos1==0) file://通道1为时隙0,则开始发送数据

begin dx<=data1[7]; file://先送高位到ST-BUS总线

dout1<=data1<<1; file://移位准备下一位待发数据

dout2<=data2;end file://准备下一通道待发数据

else if(byte_pos2==0)//通道2为时隙0,则开始发送数据(同通道1)

……

else dx<=1'bZ; end file://如果没有选择0时隙,则输出高阻,释放总线

(2)定位计数及数据发送

if(f0_flag) file://判断同步状态

begin case(bitcounter)

0:begin bitcounter<=bitsofbyte-1;//位计数器复位

if(bytecounter==(bytes_per_frame-1)) bytecounter<=0;//时隙计数满则复位

else bytecounter<=bytecounter +1;//时隙计数器递增

if(bytecounter==byte_pos1-1)

file://通道1发送数据

begin dx<=dout1[7];

file://发送数据的最高位

dout1<=dout1<<1; end

file://移位准备下一位待发数据

else if(bytecounter==byte_pos2-1) file://通道2发送数据(同通道1)

……

else dx<=1'bZ;end

file://非占用通道则释放总线

default:begin

bitcounter<=bitcounter-1;

file://位计数递减

……

file://同前面通道1、通道2发送数据

end endcase end

根据ST-BUS总线收发规则及发送模块基本工作原理,发送模块各功能块均采用C2上升沿,或者采用C2下降沿转换状态而采用C2上升沿发送数据。对前者,以上发送模块可用1个或2个always语句完成;对后者,以上发送模块则至少需用2个always语句实现,并将数据发送从以上两部分中分离出来。采用类似接收模块的方法,对发送模块单独综合后作时序仿真,结果如图3(b)所示。值得注意的是,为了说明模块设计对于通道设置顺序的无关性,图中第一通道为31时隙,第二通道为0时隙。