求此运放电路的输入阻抗和放大倍数的计算方法

时间:10-02

整理:3721RD

点击:

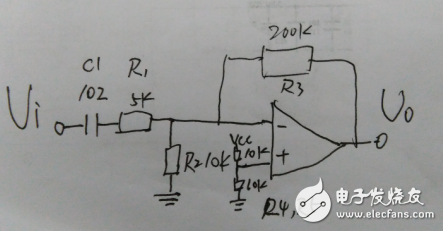

求此运放电路的输入阻抗和放大倍数的计算方法

补充内容 (2016-2-24 11:14):

该电路用于58000HZ,那么C1容坑为2.75K;R4和R5上端都有104电容接地的,目的是将输出电压抬高到1/2Vcc.

补充内容 (2016-2-24 11:14):

该电路用于58000HZ,那么C1容坑为2.75K;R4和R5上端都有104电容接地的,目的是将输出电压抬高到1/2Vcc.

模电书上应该有啊!假设运放反向端电压是u1,用它算出R2和R3的电流,通过电流可以算出Ui的表达式,然后除以R1流过的总电流就可以算出输入阻抗。

该电路用于58000HZ,那么C1容坑为2.75K,R4和R5上端都有104电容接地的,目的是将输出电压抬高到1/2Vcc.

设运放反向端为U-,根据电流守恒,有U-/10=Ui/(2.75+5)+(Uo-U-)/200,

可是计算输入阻抗和放大倍数还是没有头绪。

我算的放大关系为Uo=30.5*VCC-40*Ui,忽略电容的影响。