关于上下拉电阻大小讨论的计算

网友1:上拉或下拉取值一般选常用容易找到的阻值基本上就可以了比如4.7K10K之类的因为4.7K这种阻值市场上容易买到而且又便宜所以被广泛采用到上拉,上拉或下拉功能上也就是给一个电平信号0或者1给mcu的输入pin端口,使他在默认情况下保持一个初态。有的上拉或下拉是为了稳定信号或者补偿信号的电平,使信号高电平在长距离不低于Vcc,信号低电平不高于参考地等等。以上仅个人之见。

网友2:应该是根据电流来计算上拉或下拉电阻的阻值。

网友3:完全取决你的系统设计呢.这同时取决你的设计理念与芯片手册中IO电流驱动能力.首先,4.7k与10k比较就意味着*2的功耗.比方说在一个5v的系统下.上拉下拉工作时,可能的功耗就是5V/10k=0.1ma.整整100uA,在手持系统设计中,已经不容小觑了.100k的上拉下拉我较少看到,是否因为驱动能力太弱,为0.01ma的量级.一般来说,在电压驱动模式的电路中,100k电阻被使用吧.但是不是说,这样我们就一味选择10k电阻呢,也不是,我曾在一个项目中遇到一个现实的例子,驱动一颗逻辑IC,74HC138D时,10k上拉失败,必须选用4.7k.所以楼上2个发言综合来看就对了。

作者回复:谢谢各位理论和实践回答,综合上面例子应该是I2C和JTAG上拉与下拉问题,百度有相关答案.

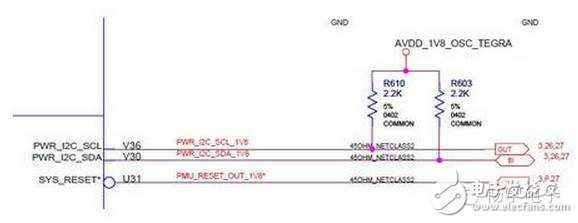

网友4:呵呵。我感觉这要看你的具体应用。1楼的说法我比较赞同,不能一概而论。这与你的负载等是有关系的。需要满足相应的电平标准,时序,还有驱动能力等。不是一概而论的。但是可能存在一种情况,比如I2C的上拉电阻,他的选取范围是比较宽的。(不考虑功耗的条件下)

作者回复:功耗与速度及初试化需求,一个热情大哥的总结.

上拉下拉。

谢谢大家!

应该说的是OC门或OD们。

数字电路的信号传递并不需要上拉下来。

按键输入可以上拉或下拉。

有人说CMOS电路输入端应该上拉下拉。

事实上肯定无此必要属于多次一举。

再次感谢大家!

开漏od门需要上拉

这个根据个人喜好,还有就是实际需要,如电流驱动能力等等

上下拉电阻的选取要看具体用在哪儿?用在控制系统,信号系统?还要看回转速率,电流,功耗等,是一个综合性和经验性质的东西,没有所谓的准确计算而言。