关于采样电阻的问题,虽然觉得简单,但还是想请教下大家,也好确认一下

时间:10-02

整理:3721RD

点击:

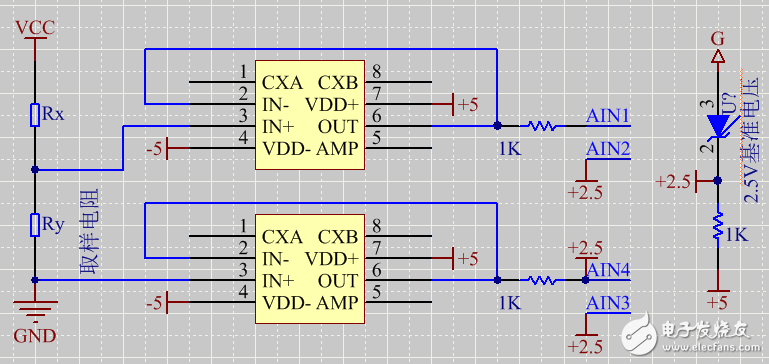

如图所示,采样电阻Ry两端接入电压跟随器进行采样。VCC和GND 和 +5、G是隔离开的,不存在回路。低压端输出接到+2.5电压,AIN1、AIN2、AIN3、AIN4为AD输入端口,其中AIN1、AIN2一对,AIN3、AIN4一对。通过AD的输出应该就可以测出Ry两端的电压。本人想请教的是,这种采样方式是差分采样吗?如果是的话,采样地应该是+2.5还是G呢?感谢各位能给予指导!

我觉得,对AD采样芯片而言,应该用“G”做参考。+2.5V是公共参考端。

而这个输入方式,不能算差分方式,两个运放起到的就是隔离抑制VCC和GND的共模噪声作用。(因为差分特性就是高共模抑制,所以整个系统有些差分的影子。)

相对与G

AIN1 范围应该是 0<AIN1<VCC

AIN4 范围应该是 0+(+2.5)<AIN1<+5V

芯片里面的计算方式应该是:

(AIN1+2.5-AIN2)-(AIN4-AIN3),如此得到的就是采样电阻的电压

因为AD口一般只能采样“正电压",AIN4加了上拉电阻,必然会引入上拉电源的干扰,而+5V系统的电源波动又是一个共模干扰,所以在AIN1引入AIN2目的也是来以AIN2或AIN3作为一个公共参考端,判断是否有电源波动!

假设,GND端引入干扰A,+5V端引入干扰B

上公式变为 (IN1+A+2.5-AIN2)-(IN4+A+2.5+B-AIN3) 因为AIN3=AIN2

变为 IN1-IN4+B

主要是采样参考电压。用哪个参考去采样,哪个就是地。

按照您的讲解,我能理解为此电路的采样地就是+2.5V吗?

你好,看了你给的回复跟我的理解有很多共同点,另外比我考虑到的要周全许多。对于提到的引入干扰这块我会着重去体会,对于输入范围也会多加验证。非常感谢!