芯片在输入信号电压高于电源电压时芯片会灌电吗?

时间:10-02

整理:3721RD

点击:

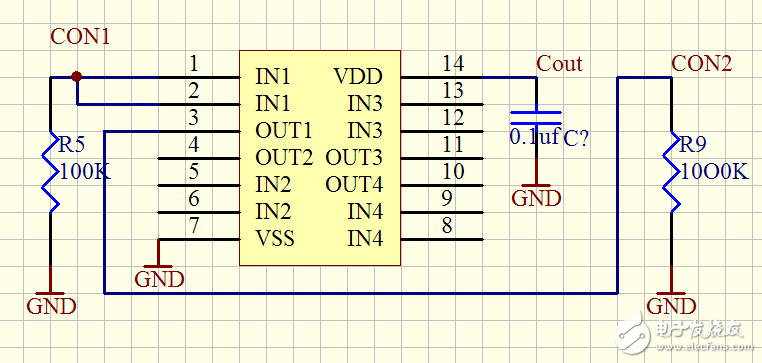

请教个问题:如果一个芯片,如果输入信号电压高于电源电压,那么芯片会正常工作吗?就像下面这个芯片当Vin1和Vin2的电压大于VDD时,芯片能正常工作吗?

补充你的问题,所以假设说你输入的处理器那端信号电平如果是5V,而这款芯片的VDD电压是max3.3V+-10%, 结果就是电流倒灌(芯片不一定损坏),这也就是电路设计的漏电所在。

当然可以。参考数据手册Vi的输入电压范围,芯片输入口内部一般会有很弱的上、下拉的,保证输入引脚悬空时的工作状态。这种情况还有一种可能,芯片供电的电源sink电流能力差,会造成Vdd被抬高。

这个。这个。这个。我不知道

谢谢你的回答啊,手册上是Vin<=Vdd+0.5V,可以工作。另外,请问是不是所有的芯片都是Vin要小于Vdd,或者最大只能比Vdd大一点,而不能大太多。如果大太多的话,会发生什么情况?不知道问题提的对不对?

我也不知道,一起学下,哈哈

芯片内部的IO端口准位电压阀值范围取决于输入的IO bat电压,你这里只有一个VDD电压,想必IO Domian电压不会超过VDD,你根据VDD的电压范围就可以推算出此芯片IO的信号电平范围了,基本浮动范围:+-10%

如果芯片Vdd=3.3V,而某个输入引脚Vin=5V,那芯片能正常工作吗

手册上没说?一般都需要进行降压变换,

这个要看这个输入脚到vdd的电源路径是否有关联,这个还是详细参考datasheet,我判断不了