解释下setup和hold time

时间:10-02

整理:3721RD

点击:

setup/hold time 是测试芯片对输入信号和时钟信号之间的时间要求。

建立时间是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间。

保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间。

Setup/hold time

Setup/hold time 是测试芯片对输入信号和时钟信号之间的时间要求,是接收器本身的特性。

如果不满足建立和保持时间的话,那么DFF(D type flip-flop/D类型触发器) 将不能正确地采样到数据,将会出现亚稳态(metastability )的情况。如果数据信号在时钟沿触发前后持续的时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量。

setup time

建立时间(setup time)是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间。输入信号应提前时钟上升沿(如上升沿有效)T 时间到达芯片,这个T 就是建立时间Setup time。简而言之,时钟边沿触发前,要求数据必须存在一段时间,这就是器件需要的建立时间。

如不满足setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器。

hold time

保持时间(hold time)是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间。简而言之,时钟边沿触发后,数据也必须保持一段时间,以便能够稳定读取,这就是器件需要的保持时间。如果hold time 不够,数据同样不能被打入触发器。

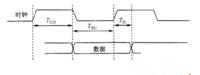

图例

以常见的触发器为例来分析其基本时序参数:建立时间、保持时间和Tco,如图所示

Setup/hold time

Setup/hold time 是测试芯片对输入信号和时钟信号之间的时间要求,是接收器本身的特性。

...[/quote]