萌新求解,关于运放两输入端细微偏差对输出的影响

时间:10-02

整理:3721RD

点击:

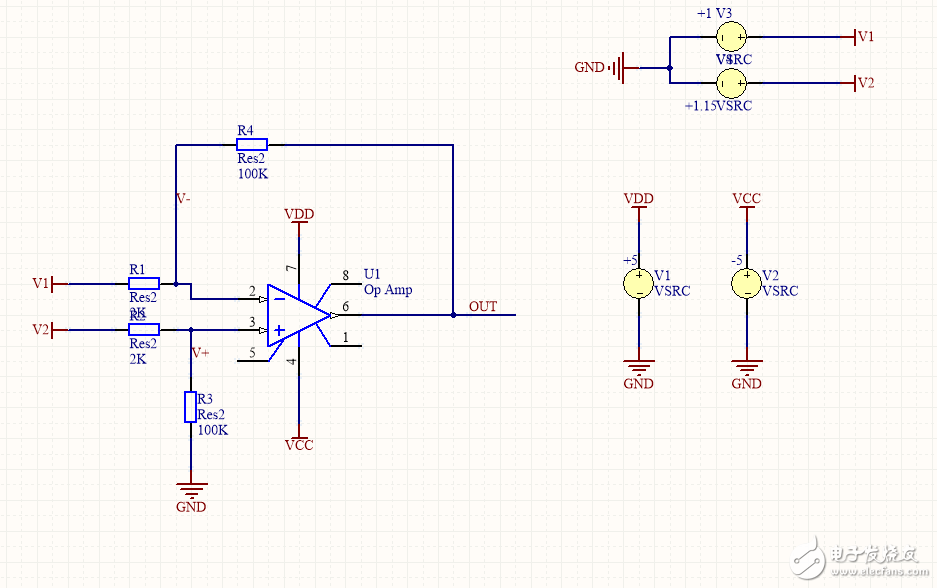

我在用ad13仿真的时候,仿真电路如图所示,理论上应该V2-V1=100mV的时候运放进入饱和,但仿真结果△V=20mV左右的时候刚好是50倍增益。△V往下减小,增益逐渐升高,检查发现V+会比V-稍低;而△V往上增加,增益会很快从50倍掉落,检查发现V+比V-要稍高。最后饱和输出大约只有2.14V。请问各路大神这是因为运放的仿真模型不对吗?可是找了半天不知道怎么去设置它的仿真参数啊。另外,我用实际的运放IC去搭电路,也发现了V+比V-低一点,增益就比理想高一点;V-比V+高一点,增益就比理想低一点的现象,请问这是怎么回事啊。