晶体管的饱和状态和饱和压降

时间:10-02

整理:3721RD

点击:

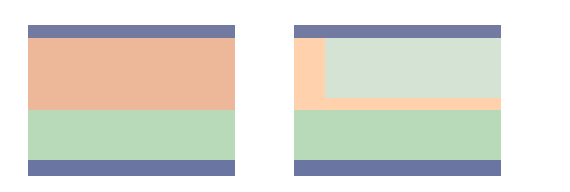

众所周知,一个普通的双极型晶体管有二个PN结、三种工作状态(截止、饱和、放大)和四种运用接法(共基、共发、共集和倒置)。对这两个PN结所施加不同的电位,就会使晶体管工作于不同的状态:两个PN结都反偏——晶体管截止;两个PN结都导通——晶体管饱和:一个PN结正偏,一个PN结反偏——晶体管放大电路(注意:如果晶体管的发射结反偏、集电结正偏,就是晶体管的倒置放大应用)。要理解晶体管的饱和,就必须先要理解晶体管的放大原理。

从晶体管电路方面来理解放大原理,比较简单:晶体管的放大能力,就是晶体管的基极电流对集电极电流的控制能力强弱。控制能力强,则放大大。但如果要从晶体管内部的电子、空穴在PN结内电场的作用下,电子、空穴是如何运动的、晶体管的内电场对电子、空穴是如何控制的等一些物理过程来看,就比较复杂了。

对这个问题,许多教课书上有不同的描述。我对此问题的理解是:当晶体管处于放大状态时,基极得到从外电源注入的电子流,部分会与基区中的空穴复合,此时产生的复合电流,构成了基极电流的主体。由于此时晶体管是处于放大状态,故集电结处于反偏。又因集电结的反偏,就在此PN结的内部,就形成了一个强电场,电场的方向由集电极指向基极,即集电极为正,基极为负。也就是说,在此PN结(集电结)联接集电极的一端,集中了大量带正电的空穴。当从基极注入的电子流进入基区后,一部分与基区内部的空穴进行了复合,而大部分电子则在强电场的作用下,被“拉”到了集电极,这种被电场“拉”到集电极的电子流,构成了集电极电流的主要组成部分。由于从基极注入的电子流,只有很少一部分在基区被复合,大部分电子是在集电结的强电场的作用下,集中到了集电极,构成了集电极电流的主体,所以,此时的集电极电流要远大于从基极注入的电流,这就是晶体管放大功能的物理模型。此时,是以NPN型晶体管进行举例。如果是PNP型晶体管,则只要把晶体管的极性由正换成负就行。

如果要从基极电流、集电极电流、发射极电流的组成、流动,PN结的能级等等方面来讲清晶体管的放大机理,就更复杂了。这在许多专业的教课书都有解释。

现在的问题是:如果增大晶体管基极的电流注入,晶体管还能工作在放大区吗?如果不能,则晶体管会从放大状态,向什么状态过渡?另外,基极电流的注入,能不能无限增加?也就是说,晶体管对基极电流有限制吗?限制的条件是什么?这就要从晶体管的放大状态,进入另一个状态的——饱和状态的讨论。在下面的讨论中,以共发射极电路进行。其它形式的放大电路,都可以用这种方法进行。

众所周知,从晶体管的发射极、基极和集电极电位的关系中,可以非常方便地对晶体管的工作状态作出判断。对处于共发射极放大的NPN型晶体管而言,集电极电位>基极电位>发射极电位时,晶体管工作于放大状态。随着基极注入电流的增大,流出该管的集电极电流也就增大。此时流过负载电阻Rc的电流同时增加。此时,因晶体管工作于放大状态,故晶体管的集电极电流可用由下式表示:

Ic=Iceo+β*ib

当忽略晶体管的反向漏电流Iceo时,

Ic≈β*ib

可见,随着基极电流的增加,集电极电流以基极电流的β倍同步增加。此时,串于集电极回路的电阻Rc上的压降,也就随着Ic增大而增大。因晶体管的集电极电位Vce=电源电压减去集电极Rc上的压降,即

Vce=Vc—Ic*Rc;

对于硅材料组成的双极型晶体管来讲,PN结的正向导通电压为0.7V,因此一般在工程中认为:当基极注入的电流,让晶体管的Ic与Rc的积满足下列公式时

(Vce-Ic*Rc)-Vb≦0V(注意:此时集电结近似零偏压,已不是原来的反偏状态了)

式中:Vce为晶体管集电极——发射极间的电压,

Vb为晶体管基极的电压。

就认为此晶体管已开始进入饱和状态。但因这时晶体管的Ic仍能随着Ib的增大而增大,只是已不符合Ic=Iceo+β*ib而已。这就是在工程中常说的“晶体管处于临界饱和状态”,又称“临界工作状态”。

此时如果继续加大基极的注入电流,晶体管的集电极电位将进一步降低,当出现晶体管的基极注入已不能使晶体管的Ic随之增大时(即(Vce-Ic*Rc)-Vb=常数时),我们就称此晶体管“进入深饱和状态”。此时,晶体管的基极电位为最高(此现象,对N-P-N晶体管而言。如果是P-N-P型晶体管,则只要在所有电源前加一负号即可得出相同的结论),即晶体管的两个PN结均处于正偏状态。

由此可以得出晶体管饱和的定义:当晶体管的两个PN结均处于正偏时,此晶体管就处于饱和状态。

在实际的放大应用中,如果放大电路是用于小信号放大,只要晶体管的静态工作点设置正确,晶体管一般不会进入饱和区。但如果晶体管放大电路处理的是信号幅值较大的信号,例音频功放的输出级,则晶体管极有可能进入饱和区。此时,就会在输出波形上出现“削顶”现象。这就是因输入信号的幅值太高,晶体管进入饱和区后,对信号失去放大作用,同时对信号产生限幅作用后的结果。

由此可得出第一个问题的答案:随着基极电流的增加,晶体管的工作状态将由放大区向饱和区过渡,当基极注入的电流达到一定程度时,晶体管的饱和程度将加深。最后出现无论基极电流怎么增加,集电极电流将维持不变,此时,晶体管进入深饱和状态。

在以上叙述中,没有提到电流的量纲问题。也就是说,晶体管在小电流工作时,同样会出现饱和状态。实际上,晶体管的静态工作点设置偏左上方时,也就是当电路的Vc较低、Rc较大时,晶体管就较容易进入饱和状态。也就是说,晶体管工作时的动态范围与所设置的晶体管工作点密切相关,而与晶体管的能流过多大的电流无关。

正想要这方面知识呢

不错不错,学习了。

学习学习

要看帖,请先回帖,养成良好的回帖习惯!

要看帖,请先回帖,养成良好的回帖习惯!

看了一下,但是还是不了解“饱和压降”到底是指什么?你能否解释一下、

对电源而言,集电结永远是反偏的,但是,当 Ie 继续增大,就会在基区拥堵泛滥,形成类似于EMOS的沟道,

基极电位高于基区电位,直至达到二极管的正向导通门限,Uce 就再也下不去了,如果施加巨幅猝发脉冲强行驱动,Uce 会反跳,这也许就是旧日的一些射频接收装置会发生 强讯号阻塞 问题的原因。

谁有用晶体管产生电子管的音响效果资料

学习一下

写的真好,谢谢分享

谁有用晶体管产生电子管的音响效果资料

要看帖,请先回帖,养成良好的回帖习惯!

PCB打样找华强 http://www.hqpcb.com 样板2天出货