谁伤害了你的硬件?剖析静电放电现象

中学物理课上用一支笔在头发上摩擦后就能吸附细小纸屑的实验一定记忆犹新,这个简单实验让我们看到了静电的存在。我们周围环境中处处存在静电,如果说我们生活在一个静电的世界里,一点也不夸张。而且,静电对于电子设备具有破坏性,稍不留神,电子设备就会因此而损坏。这绝非危言耸听!

file:///C:/DOCUME%7E1/ADMINI%7E1/LOCALS%7E1/Temp/msohtml1/01/clip_image001.jpgfile:///C:/DOCUME%7E1/ADMINI%7E1/LOCALS%7E1/Temp/msohtml1/01/clip_image001.jpg

一、无处不在的静电

物质由原子组成的,原子中有不带电的中子、带正电的质子和带负电的电子。正常状况下,一个原子的质子数与电子数量相同,正负平衡,所以对外表现出不带电的特征。但是,当两个物体相互摩擦时,产生的热量提升了电子能级,使不活泼的电子变成很容易逃逸的活泼电 子,这样的电子很快就会从一个物体转移到另一个物体中去,使两个本来处于中性的物体变成为带电的物体,这就是我们耳熟能详的“摩擦生电”现象。摩擦生电过程中,电子转移的数量和转移的速度,不仅与材料的性能差异有关,也与现场温度和湿度有关。秋冬季节,由于空气湿 度降低,分子间的黏滞力减小,运动速度加快,就很容易产生静电。我们在地板上走动、旋转转椅、开关抽屉、拿取纸笔、移动鼠标等动作都会产生静电,使我们身体和衣服上充满静电。

上面谈到的都是摩擦生电,除此之外,用电设备中还有“感应生电”和“容性生电”等静电成因。设备、电路、金属与非金属结构之间 即使不发生接触,也会通过上述两种方式产生静电。

物体间的静电感应现象即便未直接接触也会发生:CRT显示器屏幕作为一个感应源,也会在靠近它的人体上感应出静电,让使用者面部布满灰尘;两根平行导线之间因为存在寄生电容,也会在彼此间转移电荷。

二、ESD是电子设备的无形杀手

在我们的周围环境甚至我们的身上都会带有不同程度的静电,当它积累到一定程度时就会发生放电。ESD过程是处于不同电势的物体之间的静电电荷转移过程,其强烈程度受电量大小及物体间距的影响。自然界的雷电是强对流气候下典型的ESD现象日常生活中的ESD现象频繁地发生着,虽然没有大自然中的雷电那么强烈,但也会有火花式放电,不仅伴有“噼叭”声响,还会闪闪发光。寒冷干燥的冬夜里,关掉灯脱毛衣时就能真切地感受到这一现象。研究表明,当电压大于8000V时可以看到ESD发出的光亮,当电压大于6000V时可以听到ESD的放电声;当电压大于3000V时可以感觉到有ESD发生;而当静电电压低于3000V时,也会发生ESD过程,只是我们感觉不到。也就是说,很多ESD过程是在我们未察觉的情况下,悄无声息地进行着。

日常生活中的ESD现象频繁地发生着,虽然没有大自然中的雷电那么强烈,但也会有火花式放电,不仅伴有“噼叭”声响,还会闪闪发光。寒冷干燥的冬夜里,关掉灯脱毛衣时就能真切地感受到这一现象。研究表明,当电压大于8000V时可以看到ESD发出的光亮,当电压大于6000V时可以听到ESD的放电声;当电压大于3000V时可以感觉到有ESD发生;而当静电电压低于3000V时,也会发生ESD过程,只是我们感觉不到。也就是说,很多ESD过程是在我们未察觉的情况下,悄无声息地进行着。

ESD对电子设备的损害,其严重程度与静电电压高低和能量大小有关。如果能量较小,则只能将元件击穿,电压消失后,器件性能仍能恢复到原始状态。如果能量较大,在击穿后接着形成大电流对元件形成永久性损害,如晶体管元件结电阻降低、漏电流增大,薄膜电阻器局部介质击穿而发生阻值漂移等。ESD的危害有一定偶然性,不见得每一次都造成元件彻底报废,多数情况下仅表现为稳定性降低。对于静电给电子元器件造成的种种“内伤”,人们往往认为是元器件老化,而没有想到是ESD的危害。

ESD损害的严重程度还与元件对静电的敏感度有关。如今超大规模集成电路广泛采用 CMOS(复合金属氧化物半导体)材料,CMOS器件具有集成度高、成本低、速度快、能耗低的优点,因此使用范围很广。然而,CMOS器件的一个致命的弱点是静电敏感度高,很容易被ESD击穿。

ESD是电子设备故障的罪魁祸首

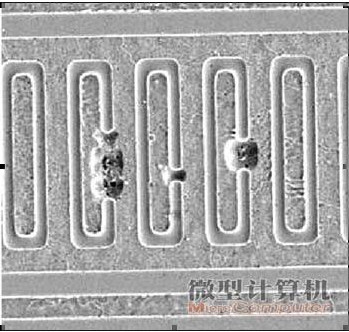

随着芯片工艺的进步,芯片的速度和功能都得以提升,但芯片却变得更加脆弱。集成度的提高使得器件尺寸越来越小,器件之间的连线宽度越来越窄,钝化层越来越薄,这些因素都会使芯片对ESD的敏感性增加。一个不太高的ESD电压就能将晶体管击穿,一个不太大的ESD电流就能将连线熔断。芯片损坏后,我们从外观上丝毫看不出有什么变化,但利用FESEM仪器却可以看清电路熔断的情形(图2)。

file:///C:/DOCUME%7E1/ADMINI%7E1/LOCALS%7E1/Temp/msohtml1/01/clip_image002.jpg

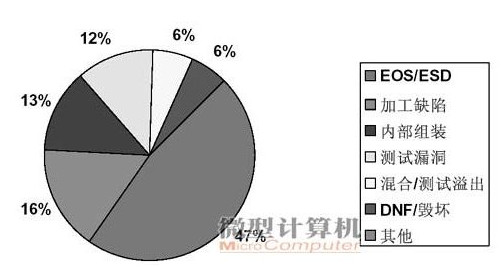

这种芯片内部的损伤,用肉眼是无法看到的。 ESD对电子设备的破坏作用具有隐蔽性、潜在性、随机性和复杂性的特点,当我们在接触电子设备时,不管是设备有静电,还是我们身体上有静电,ESD都有可能发生在接触的瞬间,可谓防不胜防。例如,来自Intel的资料表明,在引起电脑故障的诸多因素中,EOS/ESD是最大的隐患,将近一半的电脑故障都是由EOS/ESD引起的(图3)。EOS是Electrical Over Stress(电气过应力)的缩写,是过电压或过电流的总称,ESD属于EOS中的一种。

file:///C:/DOCUME%7E1/ADMINI%7E1/LOCALS%7E1/Temp/msohtml1/01/clip_image003.jpg

三、设计和制造中的防静电措施

芯片制造工艺按摩尔定律不断进步,低电压、微功耗、高集成度技术给我们带来更新的产品,而ESD对电子设备的危害性也随之增长,可以说ESD对摩尔定律继续有效将会是一个障碍,这是业界不愿看到但又不得不面对的严重问题。在电子行业中,防静电技术已经成为一个热门技术 ,防静电产品的研发和制造已经发展为一个独立的产业。

ESD防护是一个系统工程,在设计和制造阶段,可从三个方面着手:一是要防止设备本身因产生强静电感应而自我损伤,如增加屏蔽和隔离措施、通过增大PCB接地面积改善电荷泄漏通路等;二是要选择ESD特性好的芯片,不同厂家的同一种芯片性能也会有所不同,在芯片说明中一般都会提及;三是增设ESD保护电路,抵御外来静电。

1.芯片的防静电设计

随着芯片速度的提高,为了缩短引脚长度而减少信号串扰,超大规模IC芯片的封装越来越多地采用倒装芯片(flip chip),倒装芯片通常面积较大,而厚度很薄,这样芯片自身成了一个巨大的电容器,使得芯片可能携带大量静电电荷Q(=C×V)。

其次,芯片的金属盖以及散热片,是个惹是生非的祸根。诺大的金属体无异于一个静电接收天线,极易吸附芯片周围 的电场,以及芯片附近导线上的电荷,对芯片安全构成威胁。

综合上述两种不利因素,芯片的防静电设计主要从下面两个途径实现,一是采用紧密型设计技术,尽可能缩小IC核心和I/O的尺寸,以 降低寄生电容;二是采用分割器件设计的后端镇流(BEB)、整合的镇流电路(MBC)版图设计以及多触点电路设计(MFT)等,各放电通道形成相互并 联的网络,使得芯片总体等效电阻值很小,放电能力很强。

2.整机的屏蔽与接地设计

在产品的生产车间,地板、制造设备、测试仪器、芯片周转箱、库房等均为防静电设计,就连操作者也要身穿防静电服、戴上防静电手 套。但是,设备在应用过程中,ESD还是有许多的可乘之机。为了避免感应静电的危害,需要对整机进行屏蔽和接地。良好的接地措施可使设备受静电危害的几率大大降低。这样不仅可以消除外来的感应静电,也可以消除设备自身所产生的摩擦静电。当然,前提是各部件之间应该接触良好。

3.接口电路中植入ESD保护器

芯片是最容易被ESD损坏的器件,因此成为重点保护对象。而接口电路位于板卡电路的外围,是抵御ESD的一道防线。在设备的各个接口处接入ESD防护器件,使静电在防护器件上释放掉,可避免静电向电路板的纵深区域侵入。

接口电路中最简易的防静电措施是:在线路中串联一个低阻值的电阻,以限制ESD的电流,或在信号线与地线之间接入一个小电容,给 ESD电流提供通路。不过这些措施会对信号产生衰减和延迟,不利于信号传输。近几年生产的主板中,在键盘、鼠标的PS/2接口以及RS-232C串 口和IEEE 1284A并口等低速端口中,多采用内嵌防静电功能的数据收发芯片。接口芯片中内嵌的ESD保护电路,是利用寄生电路实现的。当ESD作用时,寄生电路被触发,泄放ESD电流或箝位ESD电压,达到保护目的。

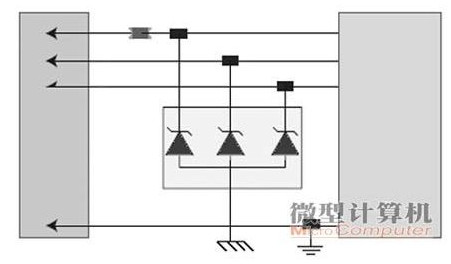

对于高速的USB和IEEE 1394热插拔接口,因为引脚较少,通常接入TVS(Transient Voltage Suppresser,瞬态电压抑制器)(图4)和 MLV(Multi-Layer Varistor,多层变阻器)等新型ESD保护器。TVS器件内通常含有若干个TVS二极管、具有多路保护作用的微型贴片元件,常见的封装形式有 SOT23和SC-70两种,最新产品有Semtech公司的MicroClamp TVS,Microsemi公司的USB50403C等。TVS能够迅速地将ESD故障电流放电到接地端,而且其漏电流和结电容都很低,响应时间也很短 (1ns左右 ),是高速数据通路中理想的选择,在各种USB设备中获得广泛应用。

file:///C:/DOCUME%7E1/ADMINI%7E1/LOCALS%7E1/Temp/msohtml1/01/clip_image004.jpg

ESD保护器虽然有多种类型,但每一种都具有“自恢复”特性,都应经得住多次放电的考验。俗话说,千里之堤,溃于蚁穴。在电路设计和制造过程中,从EMC设计到元器件筛选,从流片焊接到整机装配,不管哪个环节出了问题,都会带来防静电性能的缺陷。因此,样机设计阶段要利用好ESD测试这个查漏手段,及时发现设计漏洞,电脑整机进入包装箱前,也应按照相关标准严格测试,防止把问题产品销售出去。本文 开头提到的i865主板连续烧毁南桥芯片的质量事故,如果主板制造商进行过ESD测试,这种糟糕的事情大概就可以避免了。

四、来自“大禹治水”的启示

大禹治水的成功秘诀在于疏导为主,疏堵结合,疏中用堵,堵为疏用。前文提及,静电在我们生活中无处不在,因此我们在解决静电 问题时也应效仿大禹治水的做法,做到屏蔽和释放两种措施并举。对易受ESD危害的重点部位,应在其外围进行屏蔽和隔离;对容易积累和储存 静电的物体进行可靠接地,使静电得以及时释放。同时,还应多了解一些静电的知识,采取切实有效的防治措施,将ESD的潜在危害性降到最低 。

很好的文章,学习了。

学习了