Allegro PCB设计极速入门(一)

文章的编写目的,记录使用Allegro进行PCB设计的最笨最简单的过程(掌握这个过程,就能将PCB画完,只是效率不够高),以便快速上手并熟悉工具,进而为掌握高级自动化设计技巧打下基础。

以下是文章目录,概要说明了文章包含的内容,读者可以通读全文,了解和学习整个设计过程,也可以只读所需部分,处理遇到的问题,以便节省时间。

目录(Allegro PCB设计最精简流程与常见问题处理办法)

一、原理图相关处理(默认原理图设计完毕,进入PCB设计环节)

1、添加封装属性(操作细节)

2、原理图设计规则检查

3、导出网络表

二、PCB板边生产

1、DXF文件相关处理

2、导入DXF文件

三、导入网络表

1、基本设置

2、常见问题处理办法(symbol、pad丢失)

3、查看当前设计状态

四、PCB布局

1、显示设置

1.1、图层的开与关

1.2、鼠线的显示与关闭

2、原理图与PCB图交互式布局

3、MOVE命令

4、ROTATE命令(env文件的修改)

五、PCB布线

1、add connect命令

2、slide命令

一、原理图相关处理(默认原理图设计完毕,进入PCB设计环节)

1、添加封装属性(操作细节)

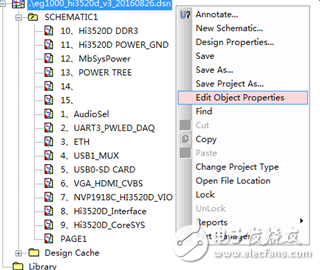

可以编辑整个工程所有元件的封装,右键点击工程,选中edit object properties

图1 编辑整个工程所有元件的封装

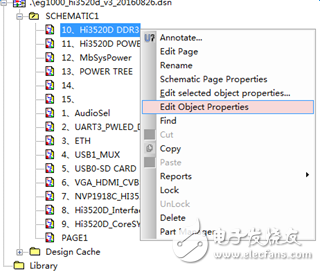

也可以编辑一张图纸里元器件的封装,右键点击原理图,选中edit object properties

图2 编辑一张图纸里元件的封装

在编辑元器件属性的时候选择orcadcapture格式比较方便些,属性栏较少,用到的主要属性栏目(如图)靠得比较近方便编辑。点击privot(该按钮可以切换属性栏的排列方式)让这些属性栏横向分布,更接近平时的BOM格式,方便编辑。

图3 选择元件属性编辑表格式

图4 元件属性标记表示意图

注意:元件的PCB Footprint属性必须和PCB封装文件名相同

2、原理图设计规则检查

导出网络表前做设计规则检查,设计规则可自主设定。

图5 规则检查窗口

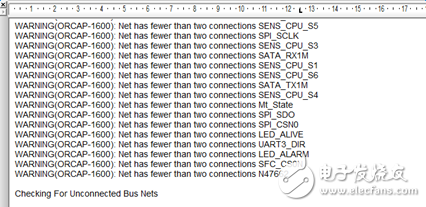

检查完毕会有session log,细看里面的每条记录,error必须得纠正,warning也得排除,看看有没有意料之外的报警。

图6 规则检查报告

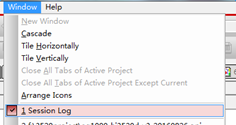

有时候session log不小心关闭了,可以在window菜单中打开。

图7 session log在菜单中的位置

3、导出网络表

排查完检查出来的问题后,可以导出网络表。

图8 网络表导出窗口

在网络表导出窗口中只需制定导出路径,软件会在路径下生成allegro和signoise.run两个文件夹,并导出网络表信息。

图9 网络表保存文件夹

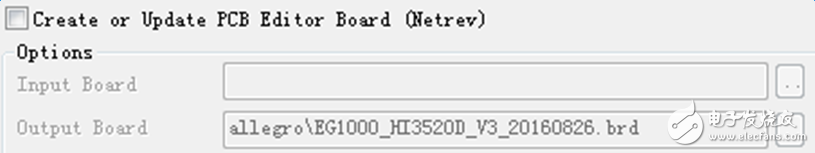

导出网络表中的create or update PCB editor board选项有点像AD9的update PCB功能,后续再研究

图10 update pcb选项

未完待续。

小编有心!请继续!