用于COB工艺的PCB设计指导

用于COB工艺的PCB设计指导

BY——黑-月

绑定角度尽量在45°之内,多于这个角度,绑定时候,银线不好打入焊盘。而且打入焊盘的尾部可能短路到相邻的焊盘,绑定焊盘之间的间距一般在4MIL为极限,半场的工艺一般就这样了。而且焊盘离被绑定的IC引脚最小在0.6MM,最大不超过3MM ,也就是他们之间。 绑定的焊盘如果分为好几层,尽量地线焊盘在最内层。一般IC部分会放一个铜皮,为地属性,所以内层焊盘尽量为地属性。信号焊盘绑在最外层,如走线。中间层为电源层,而且要留出口。绑定IC下面不能打孔,打孔绑定良率很差。

1. 目标

此文给那些正试着用裸芯片来代替表贴集成电路的PCB设计者提供了指导方针。首先,这样的转变从根本上降低了成本,即:用了裸芯片组装的线路板的总成本要比只用传统表贴元器件的线路板低。用尽可能小形体尺寸加工PCB板可确保实际的高产量。线路板上的芯片管脚所占的面积就是最小形体尺寸,因此,这里着重讲述进行COB封装时基板的布线要求。

对于电连接的设计,National公司要求 150/150 μm的线路宽度和间距,至少2层板,过孔的最小直径是350μm,过孔盘径要400μm。这些要求对于用传统技术制造PCB板的制造者来说是非常符合实际的。

2.方法

此文以两个集成IC为例,把与从SMT的PCB设计技术转换到COB的PCB设计技术相关的问题作了基本阐述。但是,对于PCB设计者来说必须从PCB制造者和装配者处得到准确的布线规则以确保达到令人满意的效果。

3. COB

芯片产品中最容易利用的形式就是裸芯片。由于这些裸芯片通过引线键合到引线框或者内部基板上,因此他们跟那些大量用于单芯片封装的芯片是一样的。用引线键合使芯片直接粘贴到PCB板上的技术称作COB。

COB是目前市场上最成熟应用最广泛的技术,具备如下特点:

a 裸芯片可以和其他封装过的芯片,分立器件或者无源器件一同直接粘贴到内部基板或者PCB上。

b 用导电或者不导电的环氧胶可使芯片固定在基板上。

c 通过引线键合可以使芯片与基板电连接。

d 可以用保护壳密封。

对于低成本COB技术,基板通常采用FR-4材料(玻璃纤维增强的环氧树脂)。推荐使用无电镀的镍/金进行表面金属化,因它能完全覆盖在金属焊盘的表面和四周,并且能够支持多种如同混合SMT/COB技术的电连接方法。

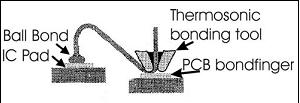

目前,对于裸芯片来说,最普遍的低成本 COB电连接技术就是引线键合。这种技术就是利用IC上标准焊盘金属化和表面钝化实现的。芯片的I/O端设计在器件外围。键合面的准确位置和尺寸连同表面冶金以供应商提供的芯片产品手册为准。COB的键合技术包括在高温下的热超声键合(金丝球焊)和常温下的超声波键合(铝劈刀焊接)。

金丝球焊是高产量,高强度的技术,它能用于精细间距焊盘的焊接。它需要高温来进行可*地焊接。此过程必须考虑配置条件、引线直径、引线长度、冶金和表面条件等。

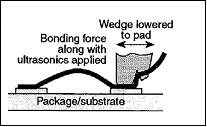

铝劈刀键合可在室温下进行,利用成本到较低的键合强度和较低的产量。键合过程中还需要考虑的就是引线键合的角度以及当用劈刀键合时向前当既有引线焊接连接方法,又涉及利用再流焊实现电连接的表贴技术时,考虑好装配次序是很重要的。封装时推荐的方法就是在装配和键合COB器件之前对表贴元器件进行装配并再流焊。值得注意的是如果表贴元器件非常*近裸芯片,那么表贴元器件的高度就会影响到引线键合的操作。通常情况下,间距应该是高度的2倍。在封装过程中,PCB设计者可查看设计规则。

4. 基板

对于低成本的装配板来说,基板技术所采用的材料几乎就属环氧玻璃钢板,例如FR4,就是用于表贴IC以及裸芯片粘贴中可供选择的材料。依据基板材料,线路板的磨光等方面权衡来实现COB,这些在布线之前就应该考虑清楚的事情本文也略加叙述。

5. 布线

用于金丝球焊接的金线直径介于20μm~33μm之间。与此相关球的直径应该是2.5到5倍的引线直径,但是对于密间距的小球焊接来说,球体直径可以是1.5-5倍;对于大的键合盘焊接,可以是3-4倍。

指状焊片的引脚被做成基板上的焊接区(指状焊片的管脚是以焊盘的形式制造在基板上的),恰好在芯片边缘外,并且与基板上的电路相连。如图1所示

Figure 1: Three bond fingers on a substrate, with interconnections to other circuitry on the substrate.Note that the bonding area is not over-coated with solder mask.

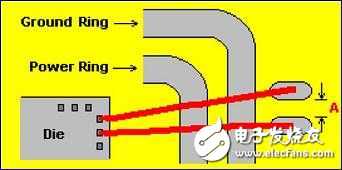

电源环和地环也包括在管脚中。图2表明管脚和芯片间的关系,其中包括一个地环和一个电源环。有的芯片要有几条地环和电源环,除了个别的电源和地线焊接点以外,这些环还应覆盖阻焊剂以避免下垂的引线和这些环相连,造成短路。

Figure 2: Bonding wire extends from I/O pad on die to interconnecting pad on substrate. The substrate bond fingers are aligned in a one to one ratio with the signal I/O pads on the die, assuming power and ground pads are connected to the rings only. The substrate footprint pads must follow the design rules for the lines and spaces on the PCB. Power and ground rings may be added within the substrate bonding pad ring.

Drawing source: Cadence Design Systems

Figure 3: Photo showing chip (on left) and wires connecting to bond fingers on substrate (right side of picture.)Photo by HKPC, courtesy of National Semiconductor.

6、指状焊片

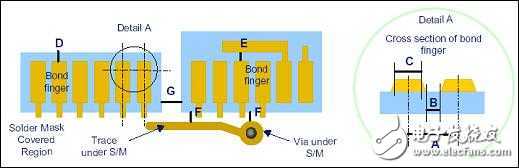

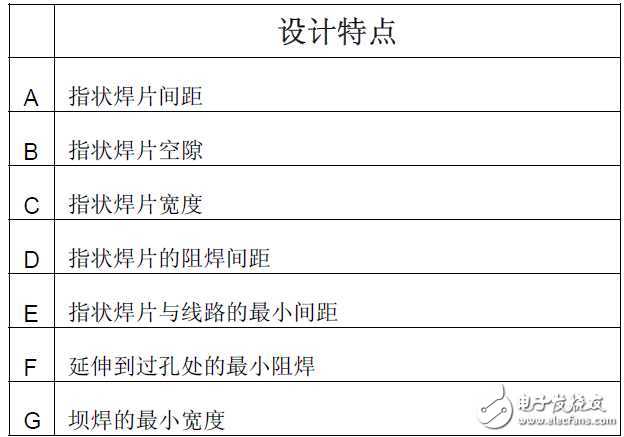

Figure 4: Bond Finger Design rule layout showing critical dimensions. Typical bondfinger length is 0.6 - 0.8 mm.

Drawing source: Infineon.

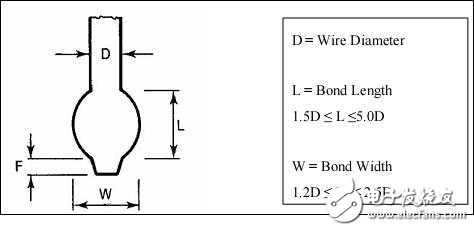

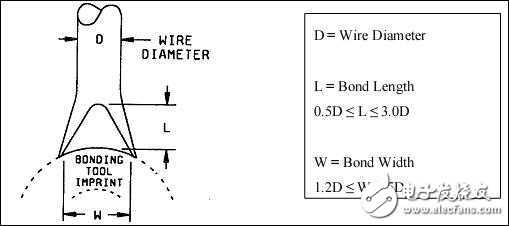

指状焊片的尺寸应该与典型的劈刀键合的焊盘尺寸或者新月形焊盘的尺寸相一致。最坏的情况也就是算上焊接工具的精准度。典型的劈刀键合如图 5所示。例如,如果引线的直径是25μm,焊盘的宽度应低于62.5μm,其长度应低于125μm 。装配工厂会提出更严格的设计规则,设计者应该事先参考这些规则。实际上,把指状焊片设计成足够几个焊盘点的长度是一个很好的习惯,这样以便于在清洁的、可焊接的表面上对这样的地点做一些返工。对于劈刀键合,焊盘的长轴应该与指定的键合线路径一致。

Figure 5: Outline view of an aluminum wedge bond showing allowable2 dimensions of the wedge.These dimensions provide a “rule of thumb” for the minimum size of the bonding pad for ultrasonic bonding of aluminum wire on the PCB. Note, however, that advances in ultrasonic systems have made it possible to produce a high-strength wedge bond that is only 2-3μm wider than the wire diameter, resulting in finer pitch capabilities.

Figure 6: Drawing3 showing wedge bonding operation on the second bond, at the substrate bond finger.

Figure 7: Tail or crescent bond is the shape of the thermosonic bond on the substrate (ball bond is on the die side). The allowable4 dimensions are shown in the box to the right of the figure. Again, these

dimensions provide a guideline for the minimum size of the bonding pad for thermosonic bonding of gold wire on the PCB.

月牙形焊接(热超声焊的末端)的尺寸和形状直接与引线直径和毛细管的几何形状有关。由于硅的收缩和更密集的引线键合间距(对焊接工具来说,这就要求越来越小的毛细管),在刀口和焊接工具的毛细管之间要有足够的平面尺寸来保证高可靠性的键合。焊接工具的外观如图7 所示。

Figure 8: Drawing showing one complete thermosonic bond. The wire is threaded through the capillary within the bonding tool and the tool tip from the capillary to the outer edge is applied to make the tail (or crescent) bond (see figure 5).

7. 指状焊片间距

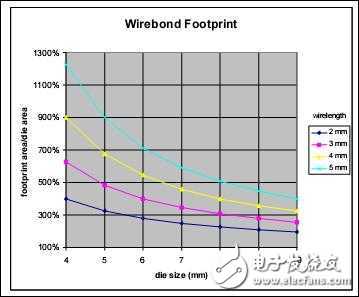

指状焊片间的间距应该足够大以避免相邻的两条引线相连而短路。引线的长度应该小于5mm来避免过分的下垂和“摆动”。在实际操作中,最大值为100D(D 是引线直径)的纵横比可以获得较高的产出。键合线的长度在芯片和基板之间的间距转换中是一个限制因素。图9表明了不同引线长度下芯片尺寸和管脚尺寸的关系。

Figure 9: Wirebond footprint area is a function of bond wire length. The maximum length of the wire is limited by the sag and “sweep” of the wire. These are a function of the length and diameter of the bonding wire.

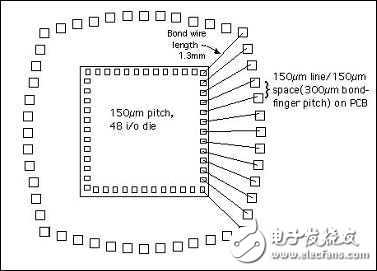

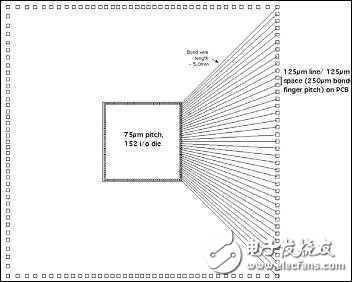

为了获得高产量的PCB 板,指状焊片的尺寸和间距应该符合PCB 制造商的标准设计要求。如果管芯之间的间距比PCB 设计规则中规定的小,指状焊片可以成放射状排列在基板上,这样,PCB 上的间距就会从各端的中心向外散开。为了增加管脚面积对芯片面积比率,折衷的办法就是键合线长度对装配PCB 效率的影响。如图10 所示。参看附录A 键合线长度的计算。

Figure 10: Drawing of 150μm pitch die with fanout to 300μm pitch bondfinger on the PCB.The drawing shows only one side of the wirebonds in place.The 300μm pitch on the PCB allows the design to stay above the minimum line and space fabrication design rules for low cost PCBs. Assuming a wire diameter of 25μm, the wire length is also well within the optimum length of 100 x diameter of the wire. Note that in this example, all bondwires are designed to be the same length. (The length is the projection of the bond wire onto the plane of the PCB surface).

芯片上硅的收缩和超密间距会使引线长度明显增加。

Figure 11: A die with very challenging feature sizes may still be accommodated by wirebonding on conventional PCBs. Up to 5mm wire length is needed at the corners to allow the space transformation of the fine pitch on die to the larger pitch on the board. 125μm line/125μm space design rules are becoming typical for low cost consumer PCB technology.

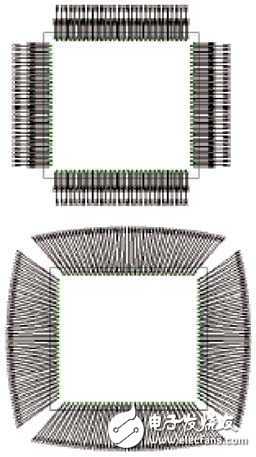

图12 表明图10 和11 中所阐述的结果。

Figure 12: Top drawing shows bondfinger pad layout orthogonally from die pads, at the same pitch. The bottom drawing shows bondfinger pads arrayed radially from die pads, resulting in relaxed pitch requirement for the PCB pads.

Drawing source: CAD Design Software: Hybrid/MCM Designer Suite

对于指状焊片的制作,如果为了适应引线和间距最小的设计规则而使引线的长度必须大于5mm,设计者可以用双排的指状焊片。如图13 所示。

Figure 13: This figure shows a staggered bond finger layout that routes the inner row (even pads 40 –62) of bond finger pads down to an inner layer of the PCB or to a power/ground ring inside the bondfinger rows. This allows support for a die with tighter pitch while respecting relaxed board fabrication and assembly design rules, as well as minimizing the board area required for the device.

Source: PWB Design Guidelines Tutorial, 10th Annual KGD Packaging and Test Workshop.

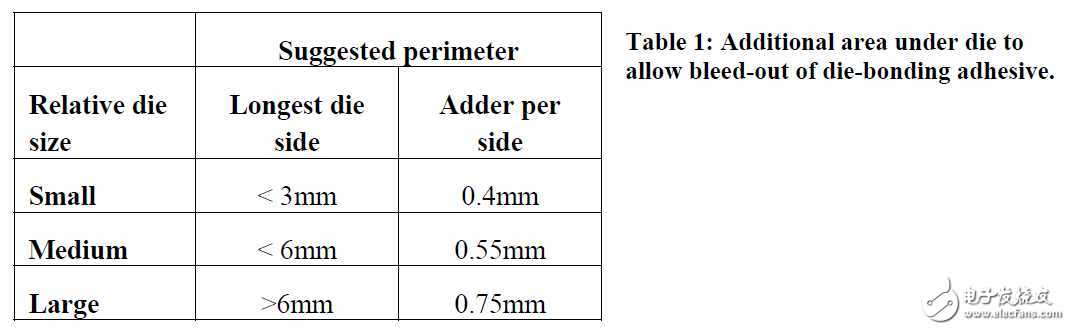

8. 芯片键合

用芯片粘合剂把芯片固定到PCB 上。在镀金的芯片焊盘周围设计出缘条时,芯片就能够可靠的固定。表1 中给出了推荐的周长

在芯片粘贴时,如果为了把电或热传导给芯片而使芯片附着的焊盘金属化,则应设有镍屏障来保护硅免受铜迁移的影响。用来粘贴和固定芯片的胶是银或金与环氧树脂的混合物,这就使胶成为电和热的导体。芯片的背面通常被设计成接地端,因此贴芯片的焊盘必须连到PCB 的电路接地端。如果背面不要求导热和导电,那么PCB 上面的阻焊剂就会为芯片附着的焊盘提供平整(panelized)的表面。

在任何情况下,为了排除由芯片粘合剂所引起的短路,指状焊片焊盘的位置与芯片焊盘的边缘至少应该有0.4-0.75mm 的距离。

为了降低精确放置元件的难度,在用于COB 生产的自动设备中,还增加了照相机。把称为基准标记的光学模板做在PCB 上,并靠照相机来校准PCB 以便实现芯片的放置、探针测试和自动光学检验。基准点标记的设计应该符合视觉系统的要求,并且要用与焊接区(焊接区是通常被用作元件焊接的部分导电图)同样的处理步骤把它放置在基板上。

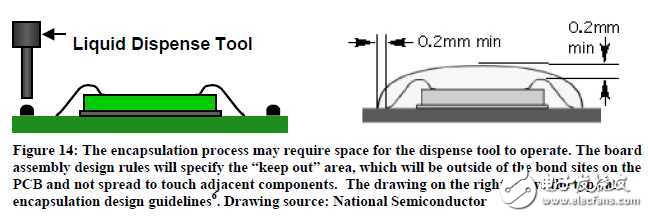

9. 密封

密封是在芯片周围形成保护壳的工艺。在大多数情况下,密封剂散布在液体中,因此,在PCB 布线时必须要给配料工具提供足够的空间使其在能够在芯片周围进行操作。如图14 所示。

由于毛细流动和泄漏的原因,在COB 设计的密封区域中是不能采用开放过孔的。

Appendix A—附录A

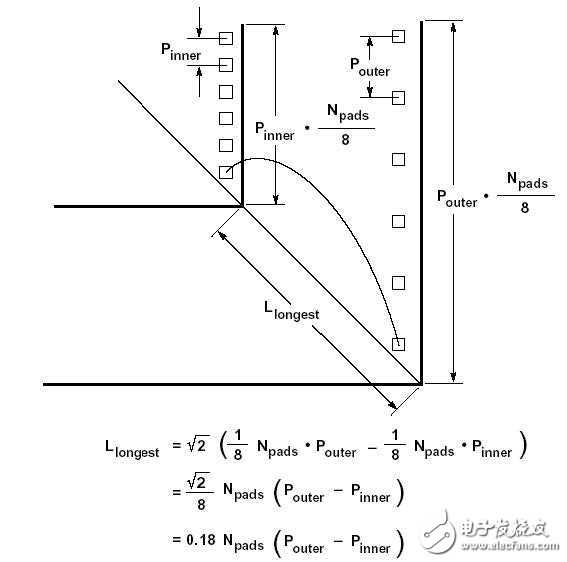

最长焊线的长度出现在芯片的顶角处,计算方法如下图所示:

Figure A-1: Longest wirebond calculation7. In the figure above, L is the projection of the wire onto the horizontal surface of the PCB, N is the number of pads on the die, Pouter is the bond finger pitch on the PCB and Pinner is the bond pad pitch on the die.

Figure A-1: Longest wirebond calculation1. In the figure above, L is the projection of the wire onto the horizontal surface of the PCB, N is the number of pads on the die, Pouter is the bond finger pitch on the PCB and Pinner is the bond pad pitch on the die.

术语表

粘合剂—类似于胶水或者水泥,使物体固定在一起的物质。在PCB 板中,用环氧树脂粘合剂来粘贴元器件使之固定到基板上。

环孔—完全围绕在孔周围的那部分导电材料。

裸芯片—无封装的分立元件或集成电路。在其上表面有焊盘,可通过引线键合或者焊接线与基板连接。

指状焊片—PCB 上的焊盘,是用于和电路元件进行引线键合连接的地方。指状焊片的数量等于连接的数量,而这些连接必须使电路元件和内层基板之间构成回路。PCB 上指状焊片布线包含了管脚。

COB—是把裸芯片焊在线路板/基板上,再从线路板到管芯用引线将彼此连接的技术。

设计规则—由PCB 制造者和装配工提出的一套指导方针,对于特殊线路板的制造或装配过程进行了详细的几何约束。

压焊—把半导体裸芯片连接到管壳或者PCB 板上,也称作芯片固定。

无电镀(淀积)--没有通电而从自身催化的电镀液中产生导电材料的淀积。

密封—通过密封或者覆盖为微电路提供机械和环境的保护。

基准点标记-- 一个在电路布线图的同一个工艺中产生的印制图特征。为相对于焊盘图的元件连接提供共用的可测量点。

管脚—PCB 上与焊盘连接的部分,可以用来进行特殊元件的装配,互连和测试。

内连基板—是一种使要连接的电子元件形成连接的基础材料和金属层。

I/O 焊盘—一个器件上的输入/输出连接结构。

(PCB 上的)焊盘--用于印刷电路板(PCB)上元件的连接或互连的那部分导电图形。

引线框—一种器件封装材料的金属部分,集成电路芯片可以表贴在上面。内引线使芯片的焊接点与管壳外部的引线相连。

间距—器件上相邻导体或I/O 焊盘的中心到中心的标称距离。

短路—致使两个或者更多的本应分开的点连接在一起的布线错误。

阻焊(S/M)--应用于PCB 表面指定区域上的耐热涂层材料,在焊接过程中可以防止焊料沉积物落在那些区域上。

热超声键合—利用超声波的能量使压力和热量结合来实现连接的方法。

过孔—穿透PCB 板的孔,镀上导电材料而使PCB 板的层与层之间构成电的连接。

超声波键合—一种利用超声频率的振动和压力的能量来实现连接的方法。

引线下垂—属焊接线故障,在其焊点之间构成随意的回路。

键合线摆动—在转移注塑或者密封过程中键合线的移动。

References

1 The National Technology Roadmap for Interconnections 2002/2003. Published by IPC, 2215 Sanders

Road, Northbrook, IL 60062-6135.

2 Zonghe Lai and Johan Liu. Effect of the Microstructure of Ni/Au Metallization on Bondability of FR-4

Substrate, The Swedish Institute of Production Engineering Research (IVF),

http://extra.ivf.se/ngl/documents/ChapterA/cobpaper.pdf

3 National Semiconductor Corporation. http://www.national.com/appinfo/die/intro_overview.html

4 Mukul Luthra. Going mainstream with chip-on-board, Circuits Assembly magazine, January 2002

5 John Lau, ed. Chip on Board: Technologies for Multichip Modules. Van Nostrand Reinhold, 1994

6 Gerald Ginsberg. Chip and Wire Technology: The Ultimate in Surface Mounting. Electronic Packaging

and Production, August 1985.

7 John Lau, ed. Chip on Board: Technologies for Multichip Modules. Van Nostrand Reinhold, 1994

8 Mil-STD-883E, Method 2010.10, 27 July 1990

9 John Lau, ed. Chip on Board: Technologies for Multichip Modules. Van Nostrand Reinhold, 1994

10 Mil-STD-883E, Method 2010.10, 27 July 1990

11 John Lau, ed. Chip on Board: Technologies for Multichip Modules. Van Nostrand Reinhold, 1994

12 John Lau, ed. Chip on Board: Technologies for Multichip Modules. Van Nostrand Reinhold, 1994

13 Tummala, ed. Microelectronics Packaging Handbook, Part II, 2nd Edition, (1997).

14 Eric Bogatin, Roadmaps of Packaging Technology. Integrated Circuit Engineering Corporation, 1997

15 Tummala, ed. Microelectronics Packaging Handbook, Part II, 2nd Edition, (1997).

16 John Lau, ed. Chip on Board: Technologies for Multichip Modules. Van Nostrand Reinhold, 1994

17 James Blankenhorn, BGA, COB and Flip Chip PCB Design. SMT Plus, Inc., 1996

18 Francis Dance, et al. Chip-On-Board Has Desings on High-Densiy Packaging. Electronic Packaging and

Production, October 1985.

19 IPC-2225 Sectional Design for Organic Multichip Modules (MCM-L) and MCM-L Assemblies. IPC,

2215 Sanders Road, Northbrook, Ill.60062

20 John Lau, ed. Chip on Board: Technologies for Multichip Modules. Van Nostrand Reinhold, 1994

21 Eric Bogatin, Roadmaps of Packaging Technology. Integrated Circuit Engineering Corporation, 1997

感谢小编分享~~~~~~~~~~~~~~~~~~

我是生产oe设备耗材劈刀切刀