高速PCB等长还有拐角等问题

时间:10-02

整理:3721RD

点击:

因为是新手,请见谅,望踊跃回答!

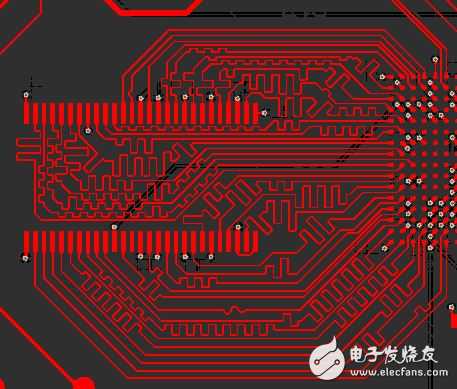

图片不是很清楚,不过能上去是直角蛇形走线,既然是蛇行走线估计是高频了,不建议走直角,建议用圆角蛇形

蛇形走线一般应用于差分信号,防止出现不等长信号延时问题

信号完整性分析操作流程

a .布线前(即原理图设计阶段)SI分析概述

用户如需对项目原理图设计进行SI仿真分析, Altium Designer要求必须建立一个工程项目名称。在原理图SI分析中,系统将采用在SI Setup Option对话框设置的传输线平均线长和特征阻抗值;仿真器也将直接采用规则设置中信号完整性规则约束,如激励源和供电网络等,同时,允许用户直接在原理图编辑环境下放置PCB Layout图标,直接对原理图内网络定义规则约束。

当建立了必要的仿真模型后,在原理图编辑环境的菜单中选择Tools -> Signal Integrity命令,运行仿真。

b .布线后(即PCB版图设计阶段)SI分析概述

用户如需对项目PCB版图设计进行SI仿真分析, Altium Designer要求必须在项目工程中建立相关的原理图设计。此时,当用户在任何一个原理图文档下运行SI分析功能将与PCB版图设计下允许SI分析功能得到相同的结果。

当建立了必要的仿真模型后,在PCB编辑环境的菜单中选择Tools -> Signal Integrity命令,运行仿真。

应该是很高深,目前看不懂,没用过SI还有没看到相关知识,所以要静静去找下书看看先

小编,关于Altium designer的信号完整性分析的能不能推荐点东西学习学习