AD6.9如何铺铜?

时间:10-02

整理:3721RD

点击:

四层板,线路连好。现在,如何让GND和VCC层铺铜?

[size=13.3333px]图1

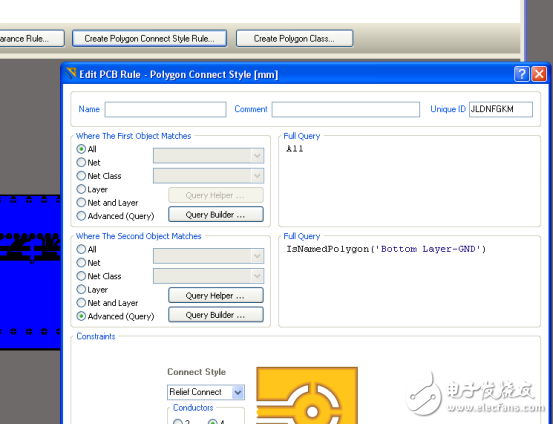

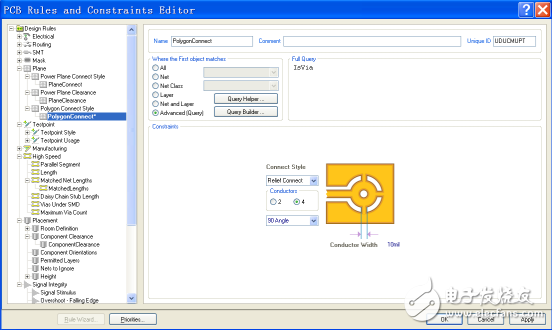

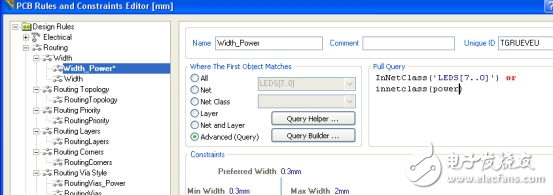

[size=13.3333px]2.在新设置的New rule 项设置过孔联接方式。"name"栏随便取个名字,在"where the first object matches"栏选"advanced(query)",

[size=13.3333px]在"full query"栏键入"IsVia",如图2所示。(该键入的信息的语法可以点击"Query Helper"来参考,如图3所示)。意思是设置过孔的联接方式。

[size=13.3333px]图2

[size=13.3333px]图3

[size=13.3333px]3.在"Connect style"栏的下拉选项中选择"direct connect"。

[size=13.3333px]如果说还想对过孔设置不一样的连接方式,只需要新建一个针对过孔的规则即可。

二.关于铜的编辑:

[size=13.3333px]首先可以正常的放置一块铜,而后在高亮点的地方随意的拖动其大小,另外如果想编辑其局部,可以单击右键:

[size=13.3333px]如此即可随意进行编辑。

三.Shelve的使用:

[size=13.3333px]在PCB编辑的过程中,可以现将所有的铜皮shelve掉,最后restore即可,这样便不会影响PCB设计的速度。

四.关于铺铜速度慢的问题:

[size=13.3333px]首先建议关掉DRC检测。另外:

[size=13.3333px]意思是在做规则设定的时候譬如间距,线宽等多用class来设定的方法,这样可以有效的提高铺铜的速度,

[size=13.3333px]这是由于在铺铜的过程中,软件会启动执行检测规则的动作。

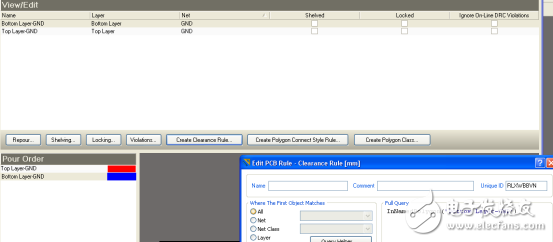

五.铺铜管理的使用:

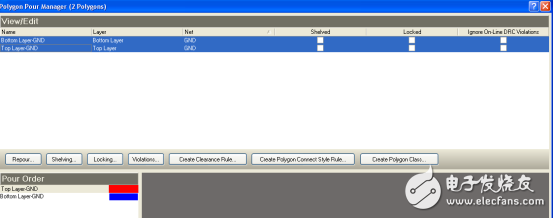

[size=13.3333px]

[size=13.3333px]在此页面里面可以轻易地查看PCB板中所有的铜皮,可以shelve,锁定,忽略DRC等的操作,

[size=13.3333px]其中比较重要的一个功能是做规则的设定:

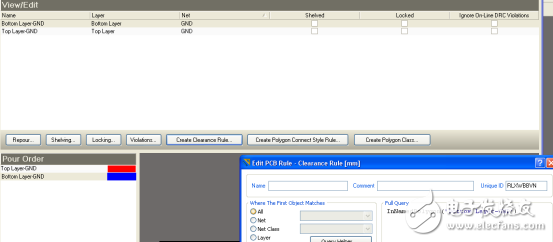

[size=13.3333px]如上图示,我们可以先选择某一块铜皮,而后点击*Create Clearance Rule*来创建间距规则,

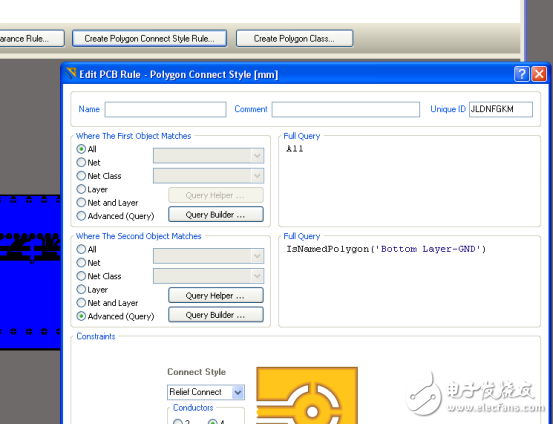

[size=13.3333px]或者是点击*Create Polygon Style Rule*来创建敷铜连接方式的规则:

信号层和内电层的本质区别在于:信号层(包括内部信号层-layer)画线的地方是铜!没画线的部分是空的!而内电层(plane)相反,画线的部分是空的,没画线的地方是铜!两种层添加种类定义是不同的!切记!

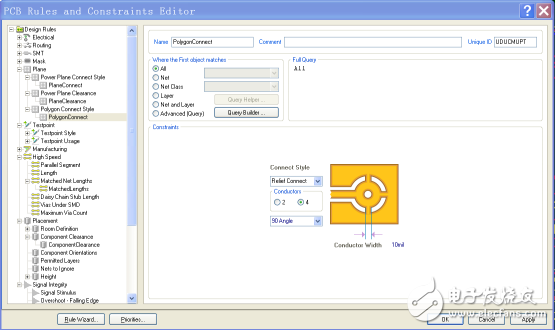

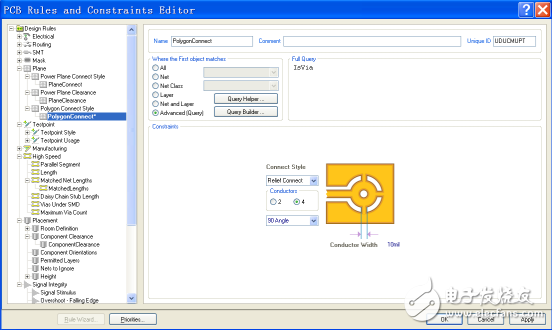

一.铜的连接方式:

[size=13.3333px]要想使铺好铜的PCB板中的过孔联接不呈十字交叉状,而是直接联接,您可以做如下操作:

[size=13.3333px]1.点击菜单Design,在下拉菜单点击Rules,找到Plane->Polygon connect style,右键点击选择New rule。出现如图1所示。

[size=13.3333px]图1

[size=13.3333px]2.在新设置的New rule 项设置过孔联接方式。"name"栏随便取个名字,在"where the first object matches"栏选"advanced(query)",

[size=13.3333px]在"full query"栏键入"IsVia",如图2所示。(该键入的信息的语法可以点击"Query Helper"来参考,如图3所示)。意思是设置过孔的联接方式。

[size=13.3333px]图2

[size=13.3333px]图3

[size=13.3333px]3.在"Connect style"栏的下拉选项中选择"direct connect"。

[size=13.3333px]如果说还想对过孔设置不一样的连接方式,只需要新建一个针对过孔的规则即可。

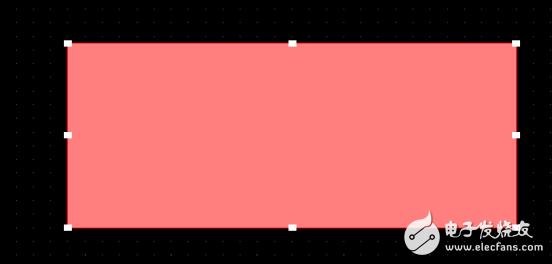

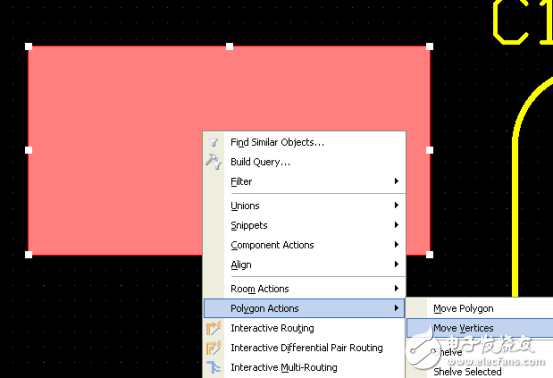

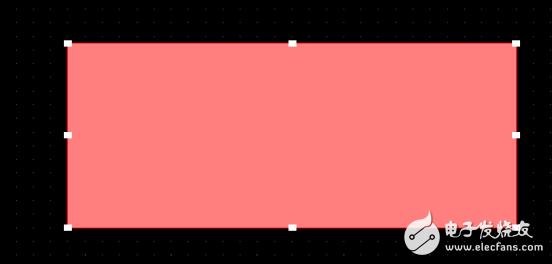

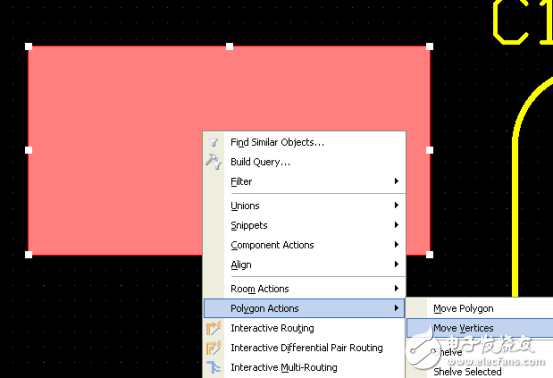

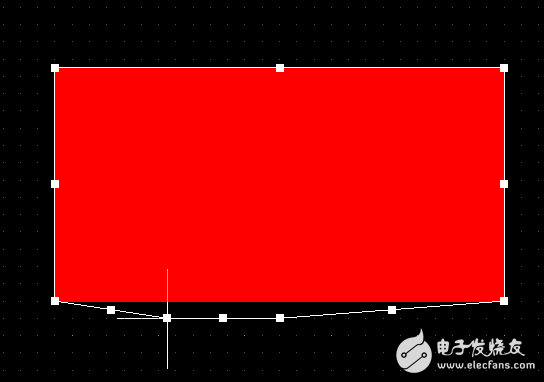

二.关于铜的编辑:

[size=13.3333px]首先可以正常的放置一块铜,而后在高亮点的地方随意的拖动其大小,另外如果想编辑其局部,可以单击右键:

[size=13.3333px]如此即可随意进行编辑。

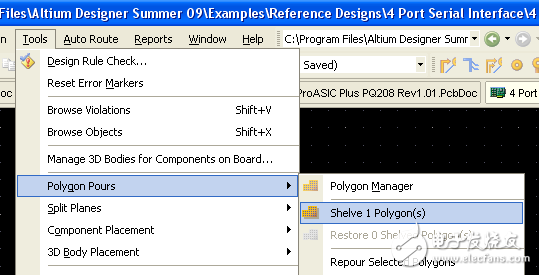

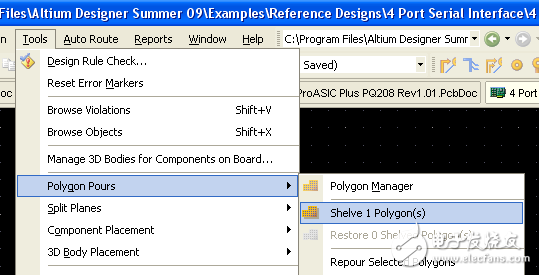

三.Shelve的使用:

[size=13.3333px]在PCB编辑的过程中,可以现将所有的铜皮shelve掉,最后restore即可,这样便不会影响PCB设计的速度。

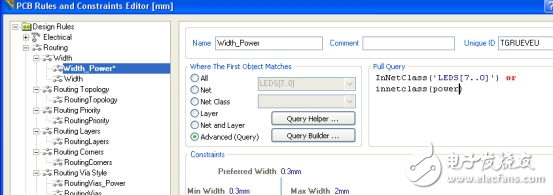

四.关于铺铜速度慢的问题:

[size=13.3333px]首先建议关掉DRC检测。另外:

[size=13.3333px]意思是在做规则设定的时候譬如间距,线宽等多用class来设定的方法,这样可以有效的提高铺铜的速度,

[size=13.3333px]这是由于在铺铜的过程中,软件会启动执行检测规则的动作。

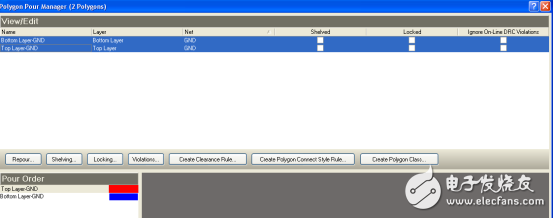

五.铺铜管理的使用:

[size=13.3333px]

[size=13.3333px]在此页面里面可以轻易地查看PCB板中所有的铜皮,可以shelve,锁定,忽略DRC等的操作,

[size=13.3333px]其中比较重要的一个功能是做规则的设定:

[size=13.3333px]如上图示,我们可以先选择某一块铜皮,而后点击*Create Clearance Rule*来创建间距规则,

[size=13.3333px]或者是点击*Create Polygon Style Rule*来创建敷铜连接方式的规则: